国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,331 - 5,340 / 6,199

半導体装置及びその製造方法

【課題】本発明は、高周波数帯で動作する半導体装置の特性の向上、ならびに信頼性の向上に関するものである。

【解決手段】半導体基板の表面側にキャリア走行層として積層された、サブコレクタ層、コレクタ層、ベース層、エミッタ層を用いて形成した単数もしくは複数のバイポーラトランジスタと、前記キャリア走行層の直下に設けられた絶縁層と、さらに前記絶縁層の直下に設けられた導電層と、前記導電層に到達するように形成された非貫通のバイアホールと、トランジスタの何れかの端子と電気的に接続された状態に半導体基板の表面に形成された金属配線層と、バイアホールの側壁及び底面に形成された金属配線層とを備えた構造とする。

(もっと読む)

薄膜トランジスタパネル

【課題】 液晶表示装置(または有機EL表示装置)において、開口率を大きくする。

【解決手段】 薄膜トランジスタ5のゲート電極11はp型またはn型不純物を含む透明な金属酸化物によって形成され、ソース電極15およびドレイン電極16は透明な金属酸化物またはITOによって形成されている。したがって、薄膜トランジスタ5は光を透過する構造となっており、この薄膜トランジスタ5のほぼ全部を画素電極4で覆っているので、薄膜トランジスタ5と画素電極4との重合部が開口率に寄与することととなり、したがって開口率を大きくすることができる。なお、ゲート電極11およびドレイン電極16の各一端部に接続された走査ライン2およびドレインライン3は、ゲート電極11およびドレイン電極16と同一の透明な材料によって形成されているが、両ライン2、3は、アルミニウム、クロムなどの遮光性金属からなる補助容量電極6によって覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムとシリコンとを含む膜で形成することで、Poly−Siと同等の仕事関数値を得るともに、下地のゲート絶縁膜とハフニウムとの反応性を低減してゲートリークを抑制し、ゲート絶縁膜の薄膜化を実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムとシリコンとを含む膜からなるものである。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 浅いソース,ドレイン接合位置を保ちつつ接合リークを低く抑えることができ

、且つコンタクト抵抗も低く保つ。

【解決手段】

SOI−MOSFETにおいて、絶縁膜102の上に形成され、チャネル領域を除いて

除去された第1のシリコン層103と、シリコン層103上にゲート絶縁膜200を介し

て形成されたゲート電極300と、シリコン層103のチャネル長方向の両側の絶縁膜1

02に設けられた溝の底面及び側面に形成され、側面の一部でシリコン層103に接する

ように形成された第2のシリコン層600と、第2のシリコン層600からなるソース,

ドレイン領域601,602上に形成されたシリサイド層631,632と、シリコン層

103と接するシリコン層600の側面部に位置するシリサイド層631,632に形成

された、AsとOを1019cm−3以上の濃度で含む拡散抑制領域とを備えた。

(もっと読む)

揮発性金属β−ケトイミナート錯体

【課題】揮発性金属β−ケトイミナート錯体及びそれを用いた電子デバイスの提供。

【解決手段】例えば2,4−ペンタンジオンとメチルアミンより得たβ−ケトイミンと塩化銅、ブチルリチウム、トリメチルビニルシランより銅β−ケトイミナート錯体を得ることができる。その銅β−ケトイミナート錯体は原子層堆積又は化学蒸着条件により基材上に金属又は金属含有フィルムを被着させるための前駆物質として使用することができる。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜へのダメージを抑制してゲートリーク電流を低減させ、且つp型ポリシリコンに近い仕事関数のゲート電極を有する半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上にゲート絶縁膜3を形成し、ゲート絶縁膜3上に450℃以下の温度でCVD法によりTiN膜4を形成し、このTiN膜4をエッチングしてゲート電極5を形成する。

(もっと読む)

エッチングプロセスのための安定化したフォトレジスト構成

【課題】エッチレイヤに特徴を形成する方法を提供する。

【解決手段】第1のマスクが前記エッチレイヤ上に形成され、前記第1のマスクは、幅を有する複数のスペースを定義する。第1のマスクは縦方向にエッチングされ、エッチングされた第1のマスクは、前記第1のマスクの前記スペースの前記幅より大きい幅を有する複数のスペースを定義する。前記エッチングされた第1のマスク上に側壁レイヤが形成され、前記側壁レイヤは、前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する複数のスペースを定義する。前記エッチレイヤ中に前記側壁レイヤを通して特徴がエッチングされ、前記特徴は前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する。前記マスク及び前記側壁レイヤは取り除かれる。

(もっと読む)

化学気相成長材料及び化学気相成長方法

【課題】 長期間の保存安定性に優れ、しかも良質なルテニウム膜を得ることができる化学的気相材料及びその化学的気相材料を用いてルテニウム膜を形成する簡易な方法の提供。

【解決手段】 下記式(1)

RuL2Y (1)

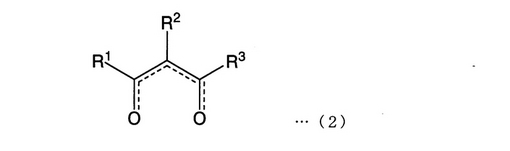

ここで、Lは下記式(2)

【化1】

で表される基であり、R1、R2及びR3は、それぞれ独立に、水素原子、フッ素原子、トリフルオロメチル基、炭素数1〜10の炭化水素基又は炭素数1〜10のアルコキシ基であり、そしてYは1,5−シクロオクタジエン、1,3−シクロオクタジエン、1,4−シクロヘキサジエン、1,3−シクロヘキサジエン、シクロペンタジエニル、1,3−ブタジエンまたは2,3−ジメチル−1,3−ブタジエンである化合物からなる化学気相成長材料。

(もっと読む)

半導体装置およびその製造方法

【課題】 メタルゲート電極を用い、かつ、信頼性が高く量産化が容易な半導体装置を提供する。

【解決手段】 半導体基板上に形成された複数のMOSFETを備え、前記複数のMOSFETのうちの少なくとも1つとしての特定のMOSFETにおけるゲート電極は、最下層の第1の金属層と、この第1の金属層の上層としてのプラチナシリサイドあるいはパラジウムシリサイドのいずれかの層と、を有するものとして構成される。

(もっと読む)

制御された処理結果分布を有するエッチング方法

本発明の実施形態は、概して、基板のエッチング方法を提供する。一実施形態において、本方法は、基板へのエッチング副生成物の均一な堆積速度に対応する基板温度ターゲットプロファイルを求める工程と、基板支持体の第2部位に対して基板支持体の第1部位の温度を優先的に調節することにより基板上でこの基板温度ターゲットプロファイルを実現する工程と、優先的に調節された基板支持体上で基板をエッチングする工程とを含む。別の実施形態において、本方法はその内部での種の分布が選択可能であり、横方向の温度制御が可能な基板支持体を有する処理チャンバ内に基板を設置し、ここで基板支持体によりもたらされた温度プロファイルと種の分布の選択が制御パラメータセットを構成している工程と、それぞれ異なる制御パラメータセットを用いて第1材料層と第2材料層をエッチングする工程を含む。

(もっと読む)

(もっと読む)

5,331 - 5,340 / 6,199

[ Back to top ]