国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,951 - 5,960 / 6,199

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

トップエミット型窒化物系発光素子及びその製造方法

本発明は、トップエミット型窒化物系発光素子とその製造方法に関し、窒化物系発光素子は、n型クラッド層と、活性層及びp型クラッド層が順次に積層されており、p型クラッド層上に形成された界面改質層と、前記界面改質層上に透明導電性素材で形成された透明導電性薄膜層と、を備えたトップエミット型窒化物系発光素子を提供する。このようなトップエミット型窒化物系発光素子及びその製造方法によれば、p型クラッド層とのオーミック接触特性が改善され、発光素子のパッケージングの際に、ワイヤーボンディング効率を、及び収率を高めることができ、低い非接触抵抗及び優れた電流−電圧特性により素子の発光効率及び素子寿命を向上することができるという長所を提供する。 (もっと読む)

半導体装置の製造方法

【課題】加工パターンの疎密に依存することなく面内均一に精度良好なパターン加工行うことが可能なエッチング工程を備えた半導体装置の製造方法を提供する。

【解決手段】基板11上にSiOCH系絶縁膜からなる被エッチング膜13を形成し、マスクパターン15上からのプラズマ処理を行う。これにより、マスクパターン15から露出している被エッチング膜13部分をSiO2化して改質部13bを形成する前処理を行う。次に、マスクパターン15およびSiOCH系材料からなる未改質部13aに対して選択的に改質部13bをエッチング除去する。

(もっと読む)

半導体装置の製造方法

【目的】 不純物の残留を抑制し、バリアメタルを高純度に成膜することを目的とする。

【構成】 基体上にTa[N((CH3)2]5を供給するTa[N((CH3)2]5供給工程(S102)と、前記Ta[N((CH3)2]5におけるTaとは異なるCを除去するH2供給工程(S106)と、前記Cが除去された前記Ta[N((CH3)2]5の吸着分子に基づいて前記TaN膜を生成するNH3供給工程(S108)と、を備え、前記Ta[N((CH3)2]5工程とH2供給工程とNH3供給工程とを繰り返すことで、前記基体上にTaN膜を堆積させることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

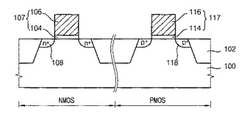

【課題】 高耐圧、低耐圧トランジスタを同一基板に備える半導体装置の、高耐圧トランジスタ領域の面積の削減を図る装置及び方法の提供。

【解決手段】 支持基板10a上の絶縁層10b上に形成された第1半導体層10cと、前記第1半導体層10c内に形成された第1高耐圧トランジスタ100Pと、前記絶縁層上に形成された第2半導体層内に形成された第2高耐圧トランジスタ100Nと、第1半導体層と第2半導体層との間に設けられた絶縁層10bに到達する深さを有する第1素子分離領域110aと、前記絶縁層10b上に形成された第3半導体層内の第1低耐圧トランジスタ200Nと、前記第3半導体層内に形成された第2低耐圧トランジスタ200Pと、前記第3半導体層内に形成され、かつ、前記第1低耐圧トランジスタ200Nと前記第2低耐圧トランジスタ200Pとの間に設けられた、前記絶縁層10bに到達しない深さを有する第2素子分離領域とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】HEMT性能を向上させる。

【解決手段】

本発明は、ヘテロ構造上で、若干のHEMTトランジスタを製造する方法と同様に、MOCVDを用いてSiN層をいささかも除去することなく、表面に接点を蒸着させることにより、構造の冷却および反応器からの試料の取り出しに先立ち、高温で成長が起こる反応器内で、最上部AlGaN層上の表面を薄いSiN層で覆うことにより、より高性能(出力)を伴い、有機金属気相成長法により成長させられた、HEMT、MOSHFET、MISHFET素子、またはMESFET素子のような、III族−N電界効果素子を製造するための新規な方法を解説している。本発明は素子も解説している。

(もっと読む)

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

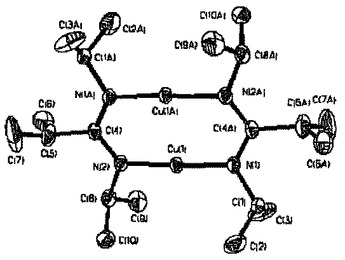

銅薄膜の堆積前駆体として有用な銅(I)化合物

半導体デバイスの製造時に銅薄膜を形成するための銅(I)アミジナート前駆体、および化学蒸着法または原子層堆積法を使用して、銅(I)アミジナート前駆体を基板上に堆積する方法を開示する。  (もっと読む)

(もっと読む)

トランジスタの製造方法、電気光学装置の製造方法、および電子デバイスの製造方法

【課題】 チャネル長の短い薄膜トランジスタを簡便に、かつ、低廉なコストで形成することができる薄膜トランジスタの製造方法を提供する。

【解決手段】 液滴乾燥法を用いることによってバンク30を形成し、このバンク30を挟んでソース電極40aとドレイン電極40bを形成する。その後、バンク30を剥離することによって得られる溝パターン50に半導体材料を供給して半導体層を形成し、ゲート絶縁膜、ゲート電極等を形成することにより、薄膜トランジスタを製造する。

(もっと読む)

5,951 - 5,960 / 6,199

[ Back to top ]