国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,981 - 5,990 / 6,199

エッチング液及びエッチング方法

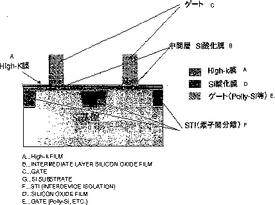

本発明は、比誘電率が8以上の膜(High−k膜)とシリコン酸化膜とが表面に形成されたものをエッチング処理するのに好適なエッチング液であって、High−k膜のエッチングレートが2Å/分以上であり、熱酸化膜(THOX)とHigh−k膜のエッチングレートの比が50以下であるものを提供する。前記エッチング液としては、フッ化水素(HF)と種々のエーテル系有機溶媒とを混合したものが好ましく使用される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ブレークダウン電圧を低電圧化しても電極の基板領域への突き抜けによるリーク電流の発生がない半導体装置を提供する。

【解決手段】 ベース領域13の表面とカソード電極15とが層間絶縁膜14bを介して電気的非接触であり、ベース領域13より接合深さが深いガードリング領域12内に埋め込まれた導電体プラグ19によりガードリング領域12とカソード電極15との電気的接触が図られているため、アルミニウムによるアロイスパイク現象が発生する虞がなくなる。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 第1層配線と、拡散層あるいはゲート電極との層間容量を抑えつつ、拡散層あるいはゲート電極に確実に接続するコンタクトプラグを形成する。

【解決手段】 基板上方に形成されたゲート電極と、ゲート電極の両側に形成された拡散層とを有する半導体装置において、一端において、ゲート電極の上面に接し、かつ、他端が、ゲート電極上面よりも、基板に近い位置に伸びる導電体膜を形成する。そして、基板上に、ゲート電極と、導電体膜とを埋め込む層間絶縁膜を形成し、この層間絶縁膜を貫通し、導電体膜の、ゲート電極上面よりも基板に近い位置において、導電体膜に接続する第プラグを形成する。

(もっと読む)

線幅の狭い半導体素子の製造方法

【課題】セルの周辺領域における線状パターンのCDを減少させることができる半導体素子の製造方法を提供する。

【解決手段】セル領域及び周辺領域が画定された基板200上にシリコン窒化膜201Aを形成する工程、シリコン窒化膜上に反射防止膜としてシリコン酸窒化膜202Aを形成する工程、セル領域では最終パターンの線幅W1Aより広い幅W1を有し、周辺領域ではパターンの崩れの発生を抑える最小の線幅W2を有するようにシリコン酸窒化膜上にフォトレジストパターン203を形成する工程、フォトレジストパターンをエッチングマスクとしてシリコン酸窒化膜とシリコン窒化膜とをエッチングする処理を、残留するシリコン酸窒化膜202Bとシリコン窒化膜201Bとの線幅W1A,W2Bがフォトレジストパターンの線幅W1,W2に比べて狭くなるまで行う工程、及び残留するシリコン窒化膜を過度エッチングする工程を含む。

(もっと読む)

発光素子

【課題】 素子面積に占める発光面積を大にでき、配光むらを抑えて高輝度化を実現することのできる発光素子を提供することにある。

【解決手段】 LED素子1の電極形成面側に、絶縁層17を介してAuからなる外部接続用のn型端子部18およびp側端子部19を設けたので、LED素子1の実装性を確保するために必要な電極形状の制約を受けることなくn−電極15およびp−電極16の形状を任意の形状で形成することができる。このことにより発光形状を考慮してp−電極16の形状を設計することが可能になり、発光面積の拡大を図ることができ、光取り出し性が向上する。

(もっと読む)

固体撮像素子の製造方法および固体撮像素子

【課題】 単層電極構造の電荷転送電極を形成するに際し、第2層導電性膜の平坦化工程に起因する膜減りを防止し、均一な膜厚の電荷転送電極を形成することにより電荷転送効率の改善を図る。

【解決手段】 ゲート酸化膜の形成された半導体基板表面に、第1の電極を構成する第1層導電性膜のパターンを形成する工程と、前記第1の電極の少なくとも側壁に電極間絶縁膜となる絶縁膜を形成する工程と、前記第1の電極および前記電極間絶縁膜の形成された前記半導体基板表面に第2の電極を構成する第2層導電性膜を形成する工程と、少なくとも前記第1の電極上の前記第2層導電性膜を除去し、平坦化する工程とを含み、前記平坦化する工程に先立ち、前記第2層導電性膜の上層の一部に除去抑制層を形成する工程を含む。

(もっと読む)

カーボンファイバーの製造方法及びそれを使用した電子放出素子の製造方法、電子デバイスの製造方法、画像表示装置の製造方法および、該画像表示装置を用いた情報表示再生装置

【課題】 良好な特性を備えるカーボンファイバーを均一性高く基体上に形成する。

【解決手段】 カーボンファイバーの製造方法であって、第1の触媒材料と、第2の触媒材料を含む触媒粒子との積層体を、基体上に配置し、第1の触媒材料と前記第2の触媒材料とを反応させることで、第1の触媒材料と第2の触媒材料とからなる触媒粒子を基体上に形成し、その後第1の触媒材料と第2の触媒材料とからなる触媒粒子と、カーボンファイバーの原料とを反応させて、基体上にカーボンファイバーを成長させる。

(もっと読む)

半導体装置

【課題】 半導体装置において、セル面積の縮小化を図ることにある。

【解決手段】 半導体装置100は、半導体基板10と、半導体基板10の内部に形成され、コントロールゲートとして機能する不純物領域22と、半導体基板10の上方に形成されたゲート絶縁層16と、ゲート絶縁層16の上方に、不純物領域22とオーバーラップして形成されたフローティングゲート18と、フローティングゲート18の上方に形成された層間絶縁層50と、層間絶縁層50の上方に、フローティングゲート18とオーバーラップして形成された遮光層52と、を含む。遮光層52は、不純物領域22と電気的に接続している。

(もっと読む)

5,981 - 5,990 / 6,199

[ Back to top ]