国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,021 - 6,030 / 6,199

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

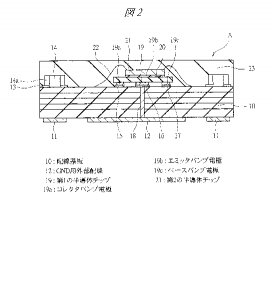

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

金属層の基板への接着及び関連する構造物

金属層を基板の表面に接着させるための方法及びそれにより得られた構造体が記載されている。該方法は、金属層を基板上に堆積する前に、該基板表面に犠牲酸性有機層を適用する工程を含む。金属層の堆積時、この犠牲酸性有機層はほぼ消費され、それにより優れた接着特性を有する金属/基板界面が残る。  (もっと読む)

(もっと読む)

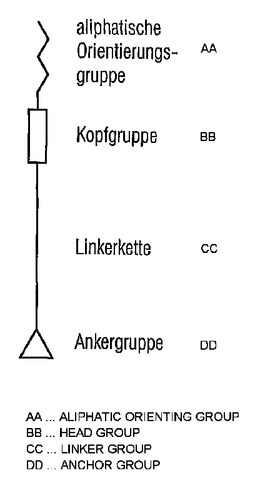

超薄膜誘電体、および、有機電界効果トランジスタでの超薄膜誘電体の使用

本発明は、基板、ソース電極、ドレイン電極、ゲート電極、および有機半導体材料を含む有機電界効果トランジスタに関するものである。このとき、誘電体層(ゲート誘電体)が、ゲート電極と半導体材料との間に配置されている。上記誘電体層は、アンカー基、リンカー基、頭部基、および脂肪族基を含んだ有機化合物の自己組織化単分子層からなる。アンカー基、リンカー基、頭部基、および脂肪族基は、この順にて互いに結合されている。  (もっと読む)

(もっと読む)

調整可能なゲート電極の仕事関数を備えたデュアルメタルのCMOSトランジスタおよびその製造方法

デュアルメタルのCMOSの配列とその形成方法は、基板(10)と、その基板(10)上に形成された複数のNMOSデバイス(44)およびPMOSデバイス(46)を提供する。複数のNMOSデバイス(44)およびPMOSデバイス(46)の各々は、ゲート電極を有する。各NMOSゲート電極は、基板(10)上に第1シリサイド領域(50)を含み、その第1シリサイド領域(50)上に第1金属領域(48)を含む。NMOSゲート電極の第1シリサイド領域(50)は、シリコンの伝導帯に近い仕事関数を有する第1シリサイド(50)からなる。PMOSゲート電極の各々は、基板上に第2シリサイド領域(54)を含み、その第2シリサイド領域(54)上に第2金属領域(52)を含む。PMOSゲート電極の第2シリサイド領域(54)は、シリコンの価電子帯に近い仕事関数を有する第2シリサイド(54)からなる。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

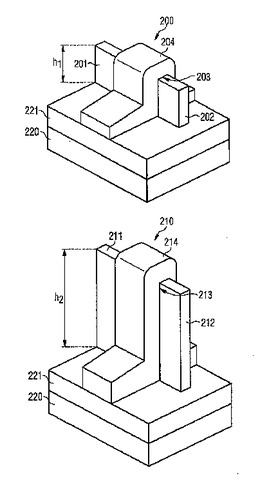

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

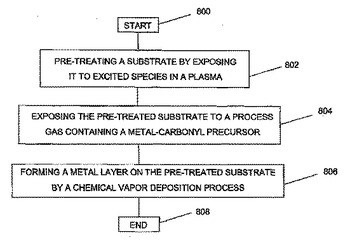

金属層を形成する方法および装置

形態が向上した金属層を基材の上に形成する方法および処理ツールが提供される。本方法は、プラズマの中で励起された化学種に基材を曝すことによって基材を前処理するステップと、金属カルボニル前駆物質を含有するプロセスガスに前処理された基材を曝すステップと、金属層を前処理された基材の上に化学蒸着法で形成するステップとを含む。金属カルボニル前駆物質は、W(CO)6、Ni(CO)4、Mo(CO)6、Co2(CO)8、Rh4(CO)12、Re2(CO)10、Cr(CO)6、またはRu3(CO)12、もしくはこれらの任意の組合せを含み、金属層は、W、Ni、Mo、Co、Rh、Re、Cr、またはRu、もしくはこれらの任意の組合せをそれぞれ含み得る。  (もっと読む)

(もっと読む)

6,021 - 6,030 / 6,199

[ Back to top ]