国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,011 - 6,020 / 6,199

金属ゲート集積化のためのゲートスタック及びゲートスタックのエッチングシーケンス

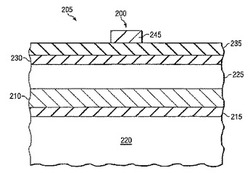

【課題】本発明は半導体デバイス(205)における金属ゲートスタック(200)を製作するためのプロセスを提供する。

【解決手段】本願の方法は、半導体基板(220)上に位置するゲート誘電体層(215)の上に金属層(210)を堆積させる段階を含む。本方法は、金属層(210)上にポリシリコン層(225)を形成する段階と、そのポリシリコン層(225)上に保護層(230)を生成する段階とを更に含む。本方法はは、また、保護層(230)上に無機反射防止被覆(235)を配置する段階を含む。他の実施形態では、金属ゲートスタックの前駆構造体及び集積回路の製造方法を含む。

(もっと読む)

セミコンダクタ・オン・インシュレータ半導体装置及び製造方法

セミコンダクタ・オン・インシュレータ半導体装置は金属又はシリサイド・ソース・コンタクト領域及びドレイン・コンタクト領域(38、40)、活性化ソース領域及びドレイン領域(30、32)並びに本体領域(34)を有する。構造体は二重ゲートSOI構造体又は完全空乏型(FD)SOI構造体でよい。スペーサ(28)を使用し、半導体層の全厚みをコンタクト領域で完全に置き換えるプロセスを用いてシャープな海面と低抵抗とが達成される。  (もっと読む)

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

スパッタ反応装置内で金属バリアを形成するために特にマルチステッププロセスで使用される可変四重電磁石アレー

スパッタチャンバ(70)及びそれが可能にするマルチステッププロセス。チャンバ軸と同軸な四重電磁石矩形アレー(72)はチャンバ内のRFコイル(46)の裏側にあることが好ましい。異なる磁場分布を生成するために、例えば、ターゲット材料をウエハ(32)上にスパッタするためにスパッタターゲット(38)が給電されるスパッタ堆積モードとRFコイルがアルゴンスパッタリングプラズマをサポートするスパッタエッチングモードとの間でコイル電流を個別に制御できる。ターゲット材料のRFコイルにおいては、コイルにDCバイアスをかけることができ、コイルアレーがマグネトロンとしての機能を果たす。このようなプラズマスパッタチャンバ内で行なわれるマルチステッププロセスは、様々な条件下でのターゲットからのバリア材料のスパッタ堆積と、基板のアルゴンスパッタエッチングとを含んでいてもよい。ターゲット電力及びウエハバイアスの減少を伴うフラッシュステップが適用される。 (もっと読む)

再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタの製作方法及び再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタ

トランジスタ製作は、基板上に窒化物ベースのチャネル層を形成すること、窒化物ベースのチャネル層上に障壁層を形成すること、窒化物ベースのチャネル層のコンタクト領域を露出させるように障壁層にコンタクト凹部を形成すること、例えば、低温堆積プロセスを使用して、窒化物ベースのチャネル層の露出されたコンタクト領域上にコンタクト層を形成すること、コンタクト層上にオーミックコンタクトを形成すること、及びオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトを形成すること、を含んでいる。また、高電子移動度トランジスタ(HEMT)及びHEMTの製作方法が提供される。HEMTは、基板上の窒化物ベースのチャネル層と、窒化物ベースのチャネル層上の障壁層と、チャネル層の中まで延びる、障壁層のコンタクト凹部と、コンタクト凹部の中の窒化物ベースのチャネル層上の窒化物ベースのn型半導体材料のコンタクト領域と、窒化物ベースのコンタクト領域上のオーミックコンタクトと、このオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトと、を含んでいる。窒化物ベースのn型半導体材料のコンタクト領域及び窒化物ベースのチャネル層は、表面積拡大構造を含んでいる。  (もっと読む)

(もっと読む)

シリサイド層を有する半導体素子の製造方法

半導体素子を形成する方法では、半導体基板を設け、絶縁層を半導体基板の上に形成し、導電層を絶縁層の上に形成し、第1金属シリサイド層を導電層の上に形成し、導電層をパターニングして、制御電極の一部分であるパターニング済み第1層を形成し、第1金属シリサイド層をパターニングしてパターニング済み第1金属シリサイド層を制御電極の上に形成してパターニング済み第1金属シリサイド層が制御電極の上に残るようにし、そして第2金属シリサイド層をパターニング済み金属シリサイド層の上に形成し、第2金属シリサイド層は第1金属シリサイド層の膜厚よりも厚い膜厚を有する。  (もっと読む)

(もっと読む)

半導体デバイス用の改良型誘電体パシベーション

半導体デバイスは、少なくとも1つの表面を含むIII族窒化物半導体材料の層と、半導体材料の電気的応答を制御するための、表面上にある制御コンタクトと、制御コンタクトに隣接する1つの表面の少なくとも一部を被覆する誘電体バリア層であって、III族窒化物のバンドギャップよりも大きなバンドギャップと、III族窒化物の導電帯からずれている導電帯とを有する、誘電体バリア層と、III族窒化物の表面の残り部分を被覆する誘電体保護層とを備えている。  (もっと読む)

(もっと読む)

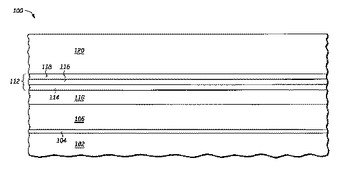

分離相補型マスクパターン転写方法

パターニング方法は、相補的なレチクルの組を個別に転写することを可能にする。一実施形態においては、例えば本方法では、位相シフトマスク(PSM)(112)をエッチングし、次にcPSMマスク(110)に対応するカットマスクをエッチングする。更に、分離相補型マスクパターン転写方法は2つの個別の、かつ分離されたマスクパターニング工程を含み、これらの工程では、像を最終ウェハパターニングの前に、複合パターンを、中間ハードマスク(112)に部分的に転写することにより形成する。中間ハードマスク材料(112)及び最終ハードマスク材料(110)は、像が最終エッチングプロセスの前に下層の基板(102)またはウェハに像が転写されることがないように選択される。  (もっと読む)

(もっと読む)

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

フィールドプレートに接続されたソース領域を有する、ワイドバンドギャップ電界効果トランジスタ

本発明に係る電界効果トランジスタは、基板(12)上に連続的に形成されるバッファ及びチャネル層(16)を備える。ソース電極(18)、ドレイン電極(20)、並びに、ソース及びドレイン電極間にあるゲート(22)はすべて、チャネル層に電気的に接続して形成される。スペーサ層(26)は、前記ゲートと前記ドレイン電極との間にあるチャネル層の表面の少なくとも一部の上に形成され、フィールドプレート(30)は、前記ゲート及びチャネル層から絶縁されるスペーサ層上に形成される。フィールドプレート(30)は、少なくとも1つの導電性パスによってソース電極に電気的に接続され、金属半導体電界効果トランジスタ内におけるピーク操作電界を低減する。  (もっと読む)

(もっと読む)

6,011 - 6,020 / 6,199

[ Back to top ]