国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,001 - 6,010 / 6,199

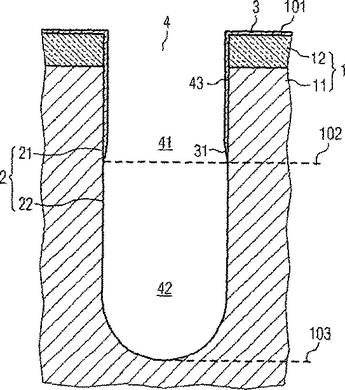

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

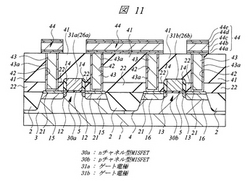

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

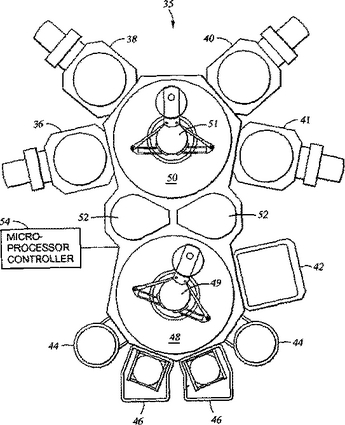

物理的気相堆積システムにおけるアニール方法及び装置

処理チャンバに配置された材料をアニールしてケイ化物層を形成するための方法及び装置が提供される。1つの態様において、シリコン材料が配置された基板を、チャンバ内の基板支持体上に配置するステップと、少なくともシリコン材料上に金属層を形成するステップと、上記基板をその場でアニールして、金属ケイ化物層を生成するステップとを備えた基板面を処理する方法が提供される。別の態様において、この方法は、ロードロックチャンバと、該ロードロックチャンバに結合された中間基板移送領域であって、第1基板移送チャンバ及び第2基板移送チャンバで構成される中間基板移送領域と、上記第1基板移送チャンバに配置された物理的気相堆積処理チャンバと、上記第2基板移送チャンバに配置されたアニールチャンバとを備えた装置において実行される。  (もっと読む)

(もっと読む)

窒素化合物含有半導体装置

【課題】 シリコン基板上に形成された窒素化合物含有半導体層を含むヘテロ構造を備え、数百V以上の高耐圧を有する窒素化合物含有半導体装置を提供する。

【解決手段】 本発明の実施の一形態に係る窒素化合物含有半導体装置は、シリコン基板と、シリコン基板上に島状に形成されたチャネル層としての第1の窒化アルミニウムガリウム(AlxGa1−xN(0≦x≦1))層と、第1の窒化アルミニウムガリウム層上に形成された第1導電型又はi型のバリア層としての第2の窒化アルミニウムガリウム(AlyGa1−yN(0≦y≦1,x<y))層と、を備えているものである。

(もっと読む)

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

金属系膜の作製方法及び金属系膜の作製装置及び積層膜作製装置

【課題】 成膜速度が速く、成膜時のダメージが小さい金属系膜の作製方法及び作製装置及び積層膜作製装置を提供する。

【解決手段】 圧力制御可能なチャンバ1に基板3を設置し、チャンバ1内に配設され、3d遷移金属からなる被エッチング部材10の上方から、B又はSiを含有するハロゲン系の原料ガスを供給すると共に、原料ガスのプラズマ19を発生させて、ハロゲンのラジカルを生成し、ハロゲンのラジカルにより、被エッチング部材10をエッチングして、被エッチング部材に含まれる3d遷移金属成分の前駆体20を生成し、被エッチング部材10より低い温度に制御された基板3に、前駆体20を成膜させると共に、成膜された前駆体20をハロゲンのラジカルにより還元して、基板3上に3d遷移金属、又は、B若しくはSiを含有する3d遷移金属の金属系膜を作製する。

(もっと読む)

半導体装置の製造方法

【課題】 電気特性評価を伴う半導体装置の製造において、半導体チップコストを増大させることなく、外部装置との組立工程で接続不良を生じない半導体装置の製造方法を提供する。

【解決手段】 半導体装置の電極パッド2に電気特性検査針4をあてて電気特性検査を行った後に、前記半導体装置の前記電極パッド2上に導電性薄膜6を形成する。

(もっと読む)

メッキ法による金属パターン形成方法

【課題】 金属集積回路構造を好適に電気鋳造する方法を提供する。

【解決手段】 本発明による方法は、中間絶縁体を貫通するビアまたはラインといった開口部(108)を形成して基板(102)の表面(104)を露出し、中間絶縁体(106)と基板の表面との上にあるベース層(110)を形成し、ベース層の上にあるストライク層(112)を形成し、ストライク層の上にある最上層を形成し、選択的にエッチングすることにより基板の表面の上にある最上層を除去してストライク層(112)の表面を露出し、ストライク層の表面の上にある金属構造(114)を電気鋳造する。電気鋳造された金属構造(114)は、電気メッキまたは無電解堆積プロセスを用いて堆積される。典型的には、この金属はCu、Au、Ir、Ru、Rh、Pd、Os、PtまたはAgである。

(もっと読む)

半導体装置およびその製造方法

【課題】 Bモード故障とシリサイド未形成による動作不良の双方を解消した半導体装置を提供する。

【解決手段】 素子分離領域により画成された第1および第2の素子領域を有する基板と、前記第1の素子領域に形成された第1のポリシリコンゲート電極を有する第1の電界効果トランジスタと、前記第2の素子領域に形成された第2のポリシリコンゲート電極を有する第2の電界効果トランジスタと、前記第1のポリシリコンゲート電極と前記第2のポリシリコンゲート電極とを結んで前記素子分離領域上を延在するポリシリコンパターンと、前記第1のポリシリコンゲート電極の表面および前記第2のポリシリコンゲート電極の表面、さらに前記ポリシリコンパターンの表面に形成され、前記第1のポリシリコンゲート電極から前記第2のポリシリコンゲート電極まで、前記ポリシリコンパターン上を延在するシリサイド層とよりなる半導体装置において、前記シリサイド層は前記ポリシリコンパターン上において層厚が増大した厚膜部を含み、前記厚膜部では、前記シリサイド層の表面が上方に突出する。

(もっと読む)

6,001 - 6,010 / 6,199

[ Back to top ]