国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

6,041 - 6,050 / 6,199

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

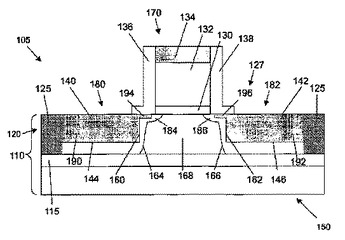

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

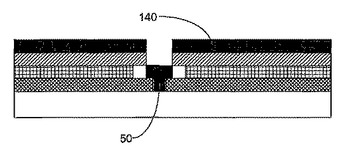

半導体製造用のゲート電極ドーパント活性化方法

一実施形態において、本発明は、一般に、基板上に堆積されたドープされた層をアニールするための方法を提供する。この方法は、ゲート酸化物層のような基板の表面に多結晶層を堆積するステップと、この多結晶層にドーパントを注入して、ドープされた多結晶層を形成するステップとを備えている。この方法は、更に、ドープされた多結晶層を急速加熱アニールに露出して、多結晶層全体にわたりドーパントを容易に分配するステップを備えている。その後、この方法は、ドープされた多結晶層をレーザアニールに露出して、多結晶層の上部のドーパントを活性化するステップを備えている。レーザアニールは、ドーパント、即ち原子を多結晶材料の結晶格子へ合体させる。 (もっと読む)

窒化物半導体装置のオーム性電極構造

窒化物半導体を有する窒化物半導体装置のオーム性電極構造であって、窒化物半導体上に形成された第1の金属膜と、第1の金属膜上に形成された第2の金属膜とを有する。第1の金属膜は、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zrから成るグループの中から選ばれた少なくとも一つの材料で構成されている。第2の金属膜は、第1の金属膜102と異なる、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zr、Pt、Auから成るグループの中から選ばれた少なくとも一つの材料で構成されている。 (もっと読む)

透明導電膜を形成する方法と装置

成膜装置は、220cm2以上の面積を有する下地(1)上にCVDによって透明導電膜を堆積するための成膜室(3)と、有機金属蒸気を含む第1のガスを輸送する第1のガス管と、酸化剤蒸気を含む第2のガスを輸送する第2のガス管と、第1と第2のガス管を結合させて第1と第2のガスを混合するためのガス混合空間(12)と、そのガス混合空間おいて混合された反応ガスを成膜室内へ導入するガス導入手段(10)と、成膜室から排ガスを排出するための排気装置(6)とを含む。 (もっと読む)

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

ショットキ・コンタクトを形成するために半導体上に導電性炭素材料を堆積するための方法、及び半導体コンタクト・デバイス

【課題】 本発明は、ショットキ・コンタクト(16)を形成するために半導体(14)上に導電性炭素材料(17)を堆積する方法に関する。

【解決手段】 本発明の方法は、半導体(14)をプロセス・チャンバ(10)内に導入するステップと、プロセス・チャンバ(10)の内部(10')を所定温度に加熱するス

テップと、プロセス・チャンバ(10)を第1所定圧力以下に減圧するステップと、プロセス・チャンバ(10)の内部(10')を第2所定温度に加熱するステップと、少なく

とも炭素を含むガス(12)を、第1所定圧力よりも高い第2所定圧力に達するまで導入するステップと、少なくとも炭素を含むガス(12)から、半導体(14)上に導電性炭素材料(17)を堆積することにより、半導体(14)上に堆積した炭素材料(17)がショットキ・コンタクト(16)を形成するステップを備えている。

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

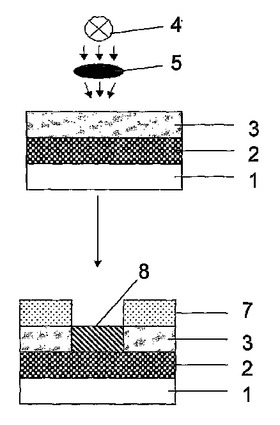

金属被着

レーザによりパターン化された基板上に金属を無電解メッキする方法。基板上に熱画像形成層および触媒層がともに被着される。レーザ・ビームで露光すると、熱画像形成層において十分なレベルの放射が熱に変換され、それによって、隣接する触媒層の露光領域が不活性になる。次いで、レーザによりパターン化された基板を反応溶液に暴露し、それによって、触媒層の非露光領域上で金属被膜の成長が開始される。  (もっと読む)

(もっと読む)

6,041 - 6,050 / 6,199

[ Back to top ]