国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

911 - 920 / 6,199

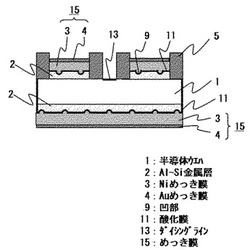

半導体装置および半導体装置の製造方法

【課題】パターン外析出を抑制し、密着力を向上させることができる半導体装置を提供する。

【解決手段】半導体ウエハ1と、半導体ウエハ1上にパターンニングして形成され最表面に複数の凹部9が形成されたAl−Si金属層2と、Al−Si金属層2上と半導体ウエハ1が露出した箇所上に形成された酸化膜11と、Al−Si金属層2上に酸化膜11を介して各凹部9を埋め込むように形成されたNiめっき膜3およびAuめっき膜4とを備える。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つソース電極及びドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、加熱処理を行う。この加熱工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設けることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発生するのを防止する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

薄膜電界効果型トランジスタの製造方法

【課題】TFT特性が良好であり、しかも面内均一性等も良好な薄膜電界効果型トランジスタを低コストで提供すること。

【解決手段】基板上に、少なくともゲート電極、絶縁膜、活性層、ソース電極およびドレイン電極が形成され、活性層上にソース電極およびドレイン電極が設けられた薄膜電界効果型トランジスタの製造方法である。本発明の製造方法は、エッチング液として、りん酸、酢酸および硝酸を含む混酸水溶液を用いて、ソース電極およびドレイン電極を形成する工程を有する。この活性層は、In、GaおよびZnを含むアモルファス酸化物半導体で構成されるものであり、かつZn濃度が20%未満であり、In濃度が40%以上であり、Ga濃度が37%以上である。

(もっと読む)

熱処理方法および熱処理装置、ならびに半導体装置の製造方法

【課題】従来技術よりも小さい熱エネルギーで、SiC基板上に低抵抗のオーミック電極を形成することができ、熱処理における半導体装置の素子部の損傷および特性の劣化を防止することができる熱処理方法および熱処理装置、ならびに前記熱処理方法を用いた半導体装置の製造方法を提供する。

【解決手段】熱処理装置1の電源部21によって、複数のパルスを含むパルス列で構成される複数パルス電流を発生させ、導線22および電流端子部23を介して、SiC基板11上の電極金属膜12に供給する。これによって電極金属膜12にジュール熱を発生させ、発生したジュール熱によって電極金属膜12を加熱する。

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の形成工程におけるフォトレジスト層を露光した際に、露光不良によりレジスト残渣が発生しないようにすること。

【解決手段】本発明の電界効果トランジスタ100は、半導体基板1上にゲート電極を備えた電界効果トランジスタで、半導体基板1上に設けられた誘電体膜2と、この誘電体膜2の開口部に設けられたフット部8と、このフット部8上及び誘電体膜2上に設けられたヘッド部9とを備え、誘電体膜の膜厚t1が、0.9k×λ/2|n1−n2|<t1<1.1k×λ/2|n1−n2|(ただしkは自然数であり、屈折率n1は所定の波長λを有する露光光に対する誘電体膜の屈折率n1(>2.1)、屈折率n2はフォトレジスト層の屈折率)である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

911 - 920 / 6,199

[ Back to top ]