国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

951 - 960 / 6,199

半導体装置の製造方法

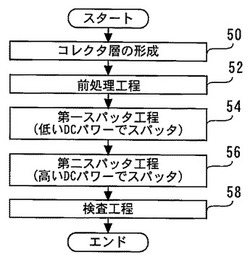

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

半導体発光素子の製造方法

【課題】発光効率と信頼性の向上

【解決手段】第2半導体層108上の全面に、透明導電膜10を形成し、形成された透明導電膜の上に、フォトレジストを塗布し、第1半導体層104の電極形成部16の上部のフォトレジストが除去される際に、除去される部分の輪郭部において、残されたフォトレジストの厚さが除去される部分に向かって次第に薄くなるようにフォトレジストを除去する。残されたフォトレジストをマスクとして、透明導電膜をウエットエッチングして、第2半導体層の一部を露出させる。残されたフォトレジスト及び透明導電膜をマスクとして、ドライエッチングして、第1半導体層の電極形成部を露出させる。残されたフォトレジストをマスクとして、透明導電膜のドライエッチングで露出した部分をウエットエッチングし、残されたフォトレジストを除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

薄膜電極、及びその製造方法

【課題】実効キャリアー濃度が増加し、物質間のエネルギーバンドギャップ調節によりショットキー障壁が減少し、高い透過率を有する、優れた電気的、光学的、熱的及び構造的特性を有する新概念のオーミック接触システムを提供する。

【解決手段】発光ダイオード又はレーザーダイオードにおいてオーミック接触を形成するための薄膜電極において、p型窒化ガリウム層上に積層され、Ni−X固溶体を含有する第1電極層と、前記第1電極層上に積層され、Au、Pt、Pd、Ni、Ru、Rh、Re、C、Cu、及びIrからなる群から選択される少なくとも1種以上の元素を含有する第2電極層と、を含むことを特徴とする、薄膜電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のオン抵抗をより低減させる。

【解決手段】第1導電型の半導体層と、前記半導体層の上側に、前記半導体層の主面に対して平行な方向に沿って周期的に配置された第1導電型の半導体ピラー領域と、前記第1導電型の半導体ピラー領域の表面に選択的に設けられた第2導電型のベース領域と、前記第2導電型のベース領域の表面に選択的に設けられたソース領域と、前記第1導電型の半導体ピラー領域間に設けられ、前記ベース領域の表面にまで達する第2導電型の半導体ピラー領域と、前記ソース領域に電気的に接続された第1の主電極と、前記半導体層の下側に設けられ、前記半導体層に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間の通電を制御する制御電極と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗体の上に急速熱酸化処理により形成され、シリサイド化ブロック用酸化膜の一部として用いる熱酸化膜の膜厚が多種のポリシリコン抵抗体間でばらつくことにより、ポリシリコン抵抗体が部分的にシリサイド化されることを回避する。

【解決手段】多種のポリシリコン抵抗体全てにおいて、急速熱酸化処理によりポリシリコン抵抗体上に生成される熱酸化膜の膜厚と、ポリシリコン抵抗体を含む非シリサイド化領域に形成された保護酸化膜の膜厚との和が、シリサイド化ブロック用酸化膜としてのブロック性能を確保するために必要な膜厚以上となるように、保護酸化膜の膜厚を決定する。多種のポリシリコン抵抗体間で急速熱酸化処理により生成される熱酸化膜の膜厚に差が生じる場合でも、熱酸化膜と保護酸化膜とをシリサイド化ブロック用酸化膜として用いることにより、充分なブロック性能を確保することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

半導体装置の製造方法および基板処理システム

【課題】 液体原料を用いてSi以外の金属膜を安定して成長させる。

【解決手段】 基板上に形成された第1の金属膜の表面を水酸基で終端する第1の前処理を行う工程と、第1の前処理後の第1の金属膜に対して水素含有ガスを供給して第2の前処理を行う工程と、第2の前処理後の第1の金属膜上に第2の金属膜を形成する工程と、を有する。

(もっと読む)

951 - 960 / 6,199

[ Back to top ]