国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

921 - 930 / 6,199

薄膜トランジスタ及びその製造方法

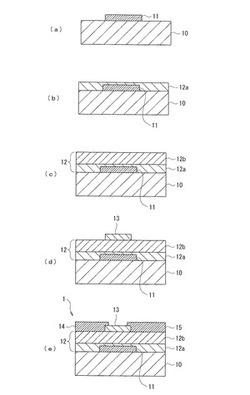

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

成膜方法及びターゲット

【課題】スパッタリング法を用いて形成されるタングステン膜の比抵抗を低下させることができる成膜方法及びこの成膜方法の実施に用いられるタングステンターゲットを提供する。

【解決手段】

タングステンを含有するターゲットTを希ガスによりスパッタしてタングステン膜を基板Sに形成する成膜方法において、ターゲットTとしてニッケルを含有するものを用いることで、成膜されたタングステン膜はニッケル酸化物を含有する。また、成膜されたタングステン膜におけるニッケルの濃度が、0.001質量%以上且つ1質量%以下となるようにする。

(もっと読む)

耐ITOピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供すること。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記Al合金膜は、Geを0.1〜5原子%含むと共に、前記Al合金膜の3倍以上のGeを含む第1層と、第1層よりもGe含有率の低いAl合金からなる第2層と、を含む積層構造を有すること。

(もっと読む)

太陽電池

【課題】入射光の利用効率が高い太陽電池の提供。

【解決手段】基材、銀電極層、光電変換層及び透明電極層がこの順に積層されてなる太陽電池であって、前記銀電極層が、下記式(1)で表わされるβ−ケトカルボン酸銀(ただし、アセト酢酸銀を除く)を含有する金属銀の形成材料が加熱されて形成された金属銀を含むことを特徴とする太陽電池[前記式(1)において、Rは直鎖もしくは分枝のC1〜C20アルキル基、またはフェニル基であり、Xは、同一であるかまたは異なり、水素原子、直鎖もしくは分枝のC1〜C20アルキル基である。]。

[化1] (もっと読む)

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

半導体ウエハ上への無電解めっきの前処理液、無電解めっき方法、及び半導体装置

【課題】n型半導体とp型半導体が混在する半導体ウエハ上へ、ニッケル又はニッケル合金の無電解めっきを行うための前処理液ろ提供する。

【解決手段】該前処理液は過酸化水素水とアンモニア水及び/又は水酸化テトラメチルアンモニウム(TMAH)からなる水溶液である無電解めっきの前処理液で、FETなどのソース、ドレイン電極など、n型半導体とp型半導体が混在するトランジスタ電極を形成する際に、シリコン基板表面の不純物を効果的に除去するか又は低減して活性化させることができ、さらにこのようなシリコン基板がn型半導体とp型半導体が混在する場合に、この洗浄液による処理を行った後、後続の無電解Ni又はNi合金めっきに適合でき、均一な無電解めっきを行うことができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】本発明は、コンタクト電極の形状を改善し、コンタクト抵抗を低くすることがで

きる。

【解決手段】 半導体基板10と、半導体基板上10に形成されたゲート絶縁膜11と、

半導体基板10上にワード線方向に沿って配置され、ゲート絶縁膜11を介して形成され

た浮遊ゲート電極12と、浮遊ゲート電極12上に第1ゲート間絶縁膜13を介して形成

された制御ゲート14を有する複数のメモリセルトランジスタMCと、ゲート絶縁膜11

上に形成されたボトム電極32と、ゲート絶縁膜11及びボトム電極32に形成された開

口EIIを通じて半導体基板10に接するトップ電極33と、開口EIIの下に形成され

、半導体基板10と逆の不純物濃度の型である接続拡散層31とを有するビット線コンタ

クトBCとを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

921 - 930 / 6,199

[ Back to top ]