国際特許分類[H01L21/322]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体の内部性質の改変,例.内部不完全性の形成 (657)

国際特許分類[H01L21/322]に分類される特許

111 - 120 / 657

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)と半導体基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。

【解決手段】溝部が設けられた半導体基板に、イオンを照射して半導体基板中に脆化領域を形成し、絶縁層を介して半導体基板とベース基板を貼り合わせると共に、半導体基板の溝部とベース基板とにより囲まれた空間を形成し、熱処理を施すことにより、脆化領域において半導体基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板等を損傷することなく、結晶欠陥形成のために行われるイオン等の照射において用いる放射線遮蔽マスクを除去する。

【解決手段】 半導体装置の製造方法は、半導体を材料とする素子形成層と、素子形成層の下面側に設けられ、開口部を有するマスク層と、素子形成層とマスク層の間に設けられ、素子形成層およびマスク層と異なる材料によって形成されている境界層と、を有する材料ウェハを準備する材料ウェハ準備工程と、マスク層の下面側から、荷電粒子の照射を行って、素子形成層に結晶欠陥を形成する結晶欠陥形成工程と、境界層と反応し、かつ、素子形成層と反応しないエッチング材を用いて、境界層をエッチングによって除去するマスク層除去工程とを含む。半導体基板等を損傷することなく、結晶欠陥形成のために行われる荷電粒子の照射において用いる遮蔽マスクを除去することが可能となる。

(もっと読む)

CMOSイメージセンサの製造方法

【課題】フォトダイオード領域の表面で発生する暗電流を低減させることのできるイメージセンサの製造方法を提供する。

【解決手段】半導体基板41上に形成されたフォトダイオード47と周辺素子とを含む半導体構造体を提供する第1ステップと、前記半導体構造体上に絶縁膜52を形成する第2ステップと、前記絶縁膜上に水素イオンを含有する水素含有誘電体膜53を形成する第3ステップと、前記水素含有絶縁層内の水素イオンを前記フォトダイオードの表面に拡散させてダングリングボンド(dangling bond)を除去する第4ステップと、前記水素含有誘電体膜を除去する第5ステップとを含んでなるCMOSイメージセンサの製造方法。

(もっと読む)

SOIウェーハの製造方法及びSOIウェーハ

【課題】ドーパントを高濃度に含有する高濃度層を有するシリコン単結晶ウェーハをベースウェーハとして使用する場合において、たとえ埋め込み酸化膜が薄くても、SOI層のドーパント濃度を制御して所望の抵抗率に調整することができ、欠陥が抑制されたSOIウェーハを製造できるSOIウェーハの製造方法を提供することを目的とする。

【解決手段】ボンドウェーハとベースウェーハとをシリコン酸化膜を介して貼り合わせを行う貼り合わせ工程と、前記ボンドウェーハを薄膜化して埋め込み酸化膜上にSOI層を形成する薄膜化工程と、前記埋め込み酸化膜の厚さを減ずる熱処理を行う工程とを含むSOIウェーハの製造方法において、前記埋め込み酸化膜の厚さを減ずる熱処理を行う工程の後に、前記SOI層中に含まれるドーパントを低減して前記SOI層の抵抗率を調整する熱処理を行う工程を有することを特徴とするSOIウェーハの製造方法。

(もっと読む)

シリコンウェーハの金属汚染試料の作製方法

【課題】半導体デバイスの製造プロセスにおける重金属汚染に伴うシリコンウェーハのゲッタリング能を高い信頼性で把握することを可能にするため、現実のデバイス後工程における重金属汚染の状態を反映した金属汚染試料を作製することができる方法を提供する。

【解決手段】重金属を添加した研磨スラリーを用い、試料用のシリコンウェーハにCMP(化学機械研磨)を施して重金属を汚染させることにより、シリコンウェーハの金属汚染試料を作製する。その際、重金属をCu、Fe、NiおよびCrのうちから選択し、研磨スラリー中の重金属の添加量を1〜1000ppbとすることが好ましい。

(もっと読む)

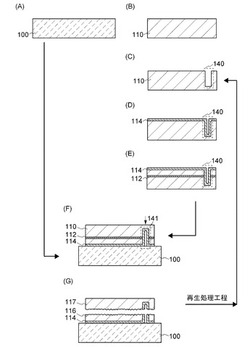

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供することを目的の一とする。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、および、半導体材料の酸化の速度および酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が選択的に除去されるエッチング処理と、損傷半導体領域が選択的に除去されるエッチング処理の後に、半導体基板の表面に研磨を行う半導体基板の再生方法である。

(もっと読む)

固体撮像装置

【課題】感度が高く且つ混色を低減した裏面照射型の固体撮像装置を実現できるようにする。

【解決手段】固体撮像装置は、半導体基板151と、半導体基板151に形成された複数の光電変換部161と、分離部163と、カラーフィルタ169と、出力回路162とを備えている。半導体基板151は、光入射面及び電荷検出面を有している。分離部163は、光電変換部161同士の間に形成され、半導体基板151に埋め込まれたシリコン層175を有する。カラーフィルタ169は、光入射面側に形成され、出力回路162は電荷検出面側に形成されている。シリコン層は、非晶質シリコン又は多結晶シリコンからなる。

(もっと読む)

基板の熱処理方法

【課題】簡易な方法で、重金属不純物を基板の系外に除去し、後工程における基板のデバイス領域の再汚染を防止できる熱処理方法を提供することを目的とする。

【解決手段】基板を熱処理する方法であって、少なくとも、前記熱処理される基板の両面を該基板から金属不純物を吸収する吸収用ウェーハで挟んだ状態で熱処理する基板の熱処理方法。前記吸収用ウェーハを、前記熱処理される基板よりも重金属に対する固溶度が高いウェーハとすることが好ましい。

(もっと読む)

エピタキシャルウェーハ及びその製造方法

【課題】 ドーパント濃度が高く、0.02Ω・cm以下のような低い抵抗率を有するP型のシリコン単結晶ウェーハにエピタキシャル層を成長させたエピタキシャルウェーハであって、従来よりもBMD密度を増大させることにより、高いゲッタリング能力を有するエピタキシャルウェーハを提供する。

【解決手段】 シリコン単結晶ウェーハの表面にエピタキシャル層を成長したエピタキシャルウェーハであって、前記シリコン単結晶ウェーハは、導電型がP型であり、抵抗率が0.02Ω・cm以下であり、前記エピタキシャル層を成長する前にRTA熱処理を施したものであり、前記エピタキシャルウェーハは、1000℃以下のデバイス熱処理を施した後のBMDサイズが20nm以上のBMD密度が5×107/cm3以上となるものであるエピタキシャルウェーハ。

(もっと読む)

固体撮像素子の製造方法

【課題】固体撮像素子の製造方法において、重金属汚染等が混入した場合にも白キズ、暗電流等の発生を抑制する。

【解決手段】固体撮像素子の製造方法は、基板に対し、600℃以上で且つ750℃以下、30分以上で且つ180分以下の第1の熱処理を行なう工程(a)と、工程(a)の後、第1の熱処理の温度よりも高い温度において熱酸化を行ない、基板上に熱酸化膜を形成する工程(b)と、工程(b)の後、基板に対し、1000℃以上で且つ1100℃以下、40分以上で且つ180分以下の第2の熱処理を行なう工程(c)と、工程(c)の後、基板に第1の不純物を導入し、光電変換部となる不純物層を形成する工程(d)とを備える。第1の熱処理の温度から熱酸化の温度に昇温する際に、4℃/分以下の昇温速度で昇温を開始する。

(もっと読む)

111 - 120 / 657

[ Back to top ]