国際特許分類[H01L21/336]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | ユニポーラ型の装置の製造のための多段階工程 (13,126) | 電界効果トランジスタ (13,024) | 絶縁ゲートを有するもの (10,315)

国際特許分類[H01L21/336]に分類される特許

81 - 90 / 10,315

半導体装置

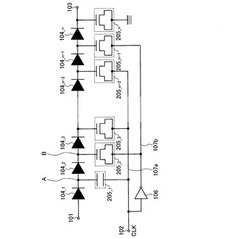

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体素子及びその製造方法

【課題】スティッキングが生じにくい半導体素子及びその製造方法を提供することを目的とする。

【解決手段】一方の面1aに触媒層3が形成された基板1において、前記一方とは反対側から前記触媒層3の裏面3aに至る開口部1cを形成する工程と、前記開口部1cにおいて、前記触媒層3の裏面3aにグラフェン5を形成する工程と、前記触媒層3の少なくとも一部を除去する工程と、を有することを特徴とする半導体素子の製造方法。開口部1cの形成後、グラフェン5の形成前に、熱処理を行うことができる。グラフェン5を形成する前に、触媒層3の表面に保護層を形成することができる。

(もっと読む)

半導体装置

【課題】結晶欠陥に起因したリーク電流を低くする。

【解決手段】ウェル106は、半導体基板100の表層に形成されており、第2導電型を有している。ドレイン拡散層130は、半導体基板100の表層に形成されており、ウェル106と接している。ドレイン拡散層130は、第1導電型を有する。ソース拡散層140はウェル106内に形成されており、第1導電型を有している。ゲート絶縁膜110は、半導体基板100半導体基板上に形成されており、平面視でドレイン拡散層130とソース拡散層140の間に位置している。ゲート電極120は、ゲート絶縁膜110上に形成されている。そして平面視で、半導体基板100は、結晶欠陥の密度が相対的に高い結晶欠陥集中領域101を有している。結晶欠陥集中領域101は、ウェル106と接していない。

(もっと読む)

酸化物半導体膜の作製方法、半導体装置の作製方法及び半導体装置

【課題】絶縁表面に形成される酸化物半導体膜は、下地界面近傍に非晶質領域が残存してしまい、これがトランジスタなどの特性に影響を与える要因の一つと考えられている。

【解決手段】酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜を形成する材料の融点を、酸化物半導体を構成する材料の融点よりも高くする。これにより、酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜との界面近傍まで結晶領域が存在することを可能とする。当該材料として絶縁性の金属酸化物を用いる。金属酸化物として、酸化物半導体膜を構成する材料と同族の材料である酸化アルミニウム、酸化ガリウムなどを用いる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に含まれる炭化珪素層の側面の面方位を特定の結晶面により近づけることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板1上に、主表面が設けられた炭化珪素層19が形成される。炭化珪素層19の主表面の一部を覆うマスク17が形成される。主表面に対して傾斜した側面SSが炭化珪素層19に設けられるように、マスク17が形成された炭化珪素層19の主表面に対して、塩素系ガスを用いた熱エッチングが行われる。熱エッチングを行う工程は、塩素系ガスの分圧が50%以下である雰囲気下で行われる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

81 - 90 / 10,315

[ Back to top ]