国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

1,061 - 1,070 / 3,836

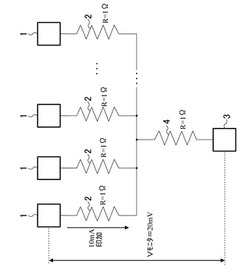

半導体装置及びその評価方法

【課題】半導体装置の回路特性の微調整に必要なトリミング情報を高精度に取得できると共に、測定時間の増大を防ぐことができるようにする。

【解決手段】半導体装置は、複数の被評価素子(TEG)2と、複数の被評価素子2のそれぞれに印加される電流値又は電圧値をモニタするモニタ用素子4と、複数の被評価素子2のそれぞれの一端と接続された複数の第1の電極パッド1と、モニタ用素子4の一端と接続された第2の電極パッド3とを有している。複数の被評価素子2のそれぞれの他端は、モニタ用素子4の他端と共通に接続されている。

(もっと読む)

半導体集積回路装置およびレイアウト方法

【課題】電源配線の近傍にビアが配置されたセルの使用が可能な半導体集積回路装置およびレイアウト方法を提供する。

【解決手段】VDD電源ストラップ311、312に接続される中間層配線21とセル列VDD電源配線11を接続する複数の電源ビア13、およびVSS電源ストラップ321、322に接続される中間層配線22とセル列VSS電源配線12を接続する複数の電源ビア13が、高密度領域、低密度領域および無配置領域に分けて配置される。その無配置領域に、電源配線付近にセル内ビアが配置されてセル面積が削減された省面積セルが配置される。

(もっと読む)

半導体デバイスモデルのモデルパラメータ抽出装置およびモデルパラメータ抽出プログラム

【課題】モデルの特性のたわみが無くなるようなモデルパラメータの抽出を実行する。

【解決手段】ビンニング処理を実行するビンニング処理部(18)と、ビンニング処理によって構成される複数のビンに対応してモデルパラメータを抽出するモデルパラメータ抽出部(11)とを具備するモデルパラメータ抽出装置(1)を構成する。モデルパラメータ抽出部(11)は、対象ビンの第1端部(A)に対応する第1モデルパラメータ(P2A)を抽出する。そして、対象ビンの第2端部(B)に対応する第2モデルパラメータ(P2B)の候補(P2B’)を、第1モデルパラメータ(P2A)に基づいて設定する。第1モデルパラメータ(P2A)と第2モデルパラメータの候補(P2B’)とに基づいて半導体デバイスの電気的特性を示す有限曲線の始点側傾斜と終点側傾斜とを特定し、それらの比較結果に基づいて、第2モデルパラメータ(P2B)を抽出する。

(もっと読む)

半導体素子

【課題】半導体素子に形成する出力パッドと内部回路の出力端子とを接続する配線の配線抵抗を抑える。

【解決手段】出力端子18の各々が基板の外周の一辺(第1の辺31)の側に沿って配列されるように基板の中央部に第1の辺31に沿って複数の内部回路16が形成される。第1の辺31に沿った領域には、複数の第1出力パッド14Aが形成され、第1の辺31に対向する第2の辺32に沿った領域には、複数の第2出力パッド14Bが形成される。複数の内部回路16の出力端子のいずれかと複数の第2出力パッド14Bのいずれかとを各々接続する複数の第2配線42の単位配線長当たりの抵抗値が、複数の内部回路16の出力端子18のいずれかと複数の第1出力パッド14Aのいずれかとを各々接続する複数の第1配線41の単位配線長当たりの抵抗値より低くなるように第2配線42の各々を形成する。

(もっと読む)

半導体集積回路

【課題】 テストの容易化が図られた半導体集積回路を提供する。

【解決手段】 組み合わせ論理回路22を構成する第1の組み合わせ論理回路22_1と第2の組み合わせ論理回路22_2との間に、第1,第2のラッチ41,42とアンドゲート43とオアゲート44とからなるスルーモード付きラッチ40を備える。スルーモード付きラッチ40は、通常動作時には第1の組み合わせ論理回路22_1から入力されたデータをスルーして第2の組み合わせ論理回路22_2に出力し、テスト動作時にはスキャンチェーンを構成する。

(もっと読む)

半導体装置、半導体装置におけるアンチヒューズ素子のプログラム方法、及び半導体装置の製造方法

【課題】周辺回路にストレスを与えずに選択したアンチヒューズ素子を確実に導通させることのできる半導体装置を提供する。

【解決手段】アンチヒューズ素子(Maf)を含み、第一及び第二の電源(VDD、VSS)から電力が供給されて動作する半導体装置であって、ソースが第三の電源(VPPSV)に、ゲートが制御ノード(AFCTL)に接続されたドライバトランジスタ(PH0)と、一端がドライバトランジスタのドレインに他端が第四の電源(VBBSV)に接続されたアンチヒューズ素子と、第一及び第二の電源に接続され、アンチヒューズ素子の抵抗値を判定する判定回路と、を備え、第三及び第四の電源の電圧を、第一の電源と第二の電源との電圧範囲外の電圧としてアンチヒューズ素子を導通させる。

(もっと読む)

半導体装置

【課題】可変論理機能を実現するための記憶回路を論理回路と等価な回路として扱うことができ、可変論理に対する機能設定の負担を部分的に軽減する。

【解決手段】可変論理機能を実現するために記憶回路と制御回路を有する機能再構成セルを複数個備え、真理値データを格納する記憶回路の読み出しアドレスを機能再構成セルそれ自体で自律的に制御する。前記制御回路は記憶回路のデータフィールド及び制御フィールドから同期的に読み出された情報を帰還入力し、制御フィールドからの帰還入力情報に基づいて、データフィールドからの帰還入力情報又は別の情報をデータフィールド及び制御フィールドを次に同期的に読み出し制御するためのアドレス情報とする。更に演算回路を備え、演算回路は、記憶回路の前記データフィールドから出力される演算制御データをデコードして演算を行う。

(もっと読む)

レイアウト検証装置、レイアウト装置、レイアウト検証方法、レイアウト検証プログラム、及び配線形成方法

【課題】シミュレーション結果に基づいて不良部分を検出する手法を用いた場合であっても、端子の位置を固定したまま配置配線データの修正を可能とする。

【解決手段】プリミティブセル群と前記プリミティブセル群に接続される接続配線との位置を示す配置配線データに基づいて、マスクに描かれるマスクパターンを示すマスクデータを取得し、前記マスクデータに基づいて前記マスクパターンの位置を検証し、エラー部分を検出する検証手段と、前記エラー部分に基づいて修正ヒント情報を生成し、前記配置配線データを修正する配置配線手段に対して前記修正ヒント情報を通知する修正ヒント作成手段とを具備し、前記修正ヒント作成手段は、前記プリミティブセル群に含まれる端子群の位置を示す端子情報を取得し、前記端子情報に基づいて、前記端子の位置が前記配置配線手段により変更されないように、前記修正ヒント情報を生成する。

(もっと読む)

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】機能を柔軟に制御可能なアナログの機能ICを提供する。

【解決手段】アナログブロック10は、所定のアナログ信号処理を実行する。デジタルブロック20は、再構成可能に構成され、所定のデジタル信号処理を実行してアナログブロック10を制御する。FeRAM30は、デジタルブロック20の回路構成のコンフィギュレーションデータを格納する。機能IC100は、FeRAM混載プロセスを用いてひとつの半導体基板上に一体集積化され、アナログブロック10の動作状態が、デジタルブロック20の構成状態に応じて変更可能である。

(もっと読む)

1,061 - 1,070 / 3,836

[ Back to top ]