国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

11 - 20 / 3,836

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

設計支援装置

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

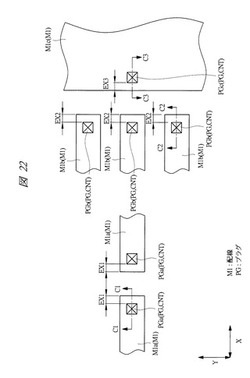

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

クロック分配回路

【課題】フィードバックパスのバラツキの影響を最小限に抑え、クロックの位相の調整を高精度に行うことができるクロック分配回路を提供する。

【解決手段】クロック分配回路21は、クロック信号を生成するクロック生成回路、前記クロック信号が分配されるクロック分配網22、前記クロック分配網の分岐点N1を通じて分配されるクロック信号で動作する順序回路26、を有する。クロック分配回路は更に、前記分岐点から分岐した前記クロック信号をフィードバック信号として入力し、該入力したフィードバック信号とリファレンスクロック信号とに基づいて、前記クロック信号を前記クロック分配網へ出力するクロック生成回路を有する。前記分岐点は、前記クロック分配網の順序回路の前段のクロックドライバ25のうち、前記クロック生成回路の近傍にあるクロックドライバに設けられる。

(もっと読む)

11 - 20 / 3,836

[ Back to top ]