国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

81 - 90 / 3,836

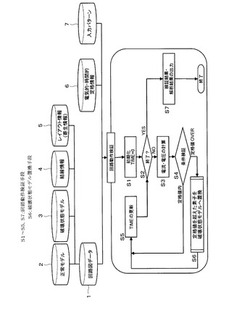

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

消費電流算出装置、消費電流算出プログラムおよび消費電流算出方法

【課題】ミックスドシグナル回路の消費電流を短時間で見積もること。

【解決手段】消費電流算出装置100は、対象回路へ入力されるデジタル信号の値113と、デジタル信号とともに対象回路へ入力されるアナログ信号の値112と、を取得する。消費電流算出装置100は、デジタル信号の値113およびアナログ信号の代表値の組み合わせごとに組み合わせが入力された場合の対象回路の消費電流を示す消費電流テーブル114から、デジタル信号の値113が対象回路へ入力された場合のアナログ信号の各代表値と消費電流との対応情報115を抽出する。消費電流算出装置100は、抽出した対応情報115に基づいて、アナログ信号の各代表値の間の値に対応する対象回路の消費電流を補間する補間関数116を生成し、生成した補間関数116に基づいて、アナログ信号の値112に対応する対象回路の消費電流117を算出する。

(もっと読む)

LSIのレイアウトパターン表示装置および表示方法

【課題】レイアウトパターン上で、直観的に回路素子を認識可能とし、回路素子間の信号の流れの把握を容易にする。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。条件設定部800には、セル枠決定に用いる特定のレイヤーを示す情報がセル枠決定条件として設定されており、セル枠決定部600は、個々のセルについて、当該特定のレイヤーに収録されている図形を抽出し、抽出した図形の論理和図形を形成し、この論理和図形の外接矩形をセル枠として求める。端子図形生成部500は、求めたセル枠とセル間配線との交差位置に端子図形を生成する。レイアウトパターン表示部400は、セル枠と端子図形をレイアウトパターン上に重畳表示する。

(もっと読む)

遅延時間計算プログラム、装置及び方法

【課題】遅延時間計算プログラム、装置及び方法において、回路におけるネットの遅延時間を高精度に計算することを目的とする。

【解決手段】回路内のネットの遅延時間を計算する遅延時間計算処理は、ネットが第1の条件を満たす場合にネットの遅延時間を計算するための第1の遅延計算手順を選択する第1の手順と、第1の手順で第1の遅延計算手順が選択されない場合、第2の条件をネットが満たすか否かに応じて、第1の遅延計算手順及びネットの遅延時間を計算するための第2の遅延計算手順のいずれか一方を選択する第2の手順と、第1の手順或いは第2の手順のいずれかで選択された遅延計算手順によりネットの遅延時間を計算する第3の手順を含むように構成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

配置配線装置

【課題】改訂期間の短縮およびマスク改定費用の削減を図ることが可能な配置配線装置を提供すること。

【解決手段】比較部32は、既存ネットおよび改訂情報から論理の改訂箇所を特定し、論理を合わせるための論理接続情報を抽出する。判定部33は、レイアウト情報および比較部によって抽出された論理接続情報に基づいて、メタル層の最上位層から順に配線の繋ぎ換えの可否を判定する。そして、置換部34は、判定部33によって繋ぎ換えが可能と判定されたメタル層において配線の繋ぎ換えを行なう。したがって、上位層のみの改訂によって改訂期間の短縮およびマスク改定費用の削減を図ることが可能となる。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

回路のレイアウト装置,処理方法およびプログラム

【課題】 回路のレイアウト装置で,EOEの発生しやすい箇所を推定することを目的とする。

【解決手段】 回路レイアウト装置1は,被研磨対象となる回路の配線パターンを含む回路情報を取得する回路情報取得部11,回路を任意の単位領域でメッシュ状に区切り,各メッシュ領域について,メッシュ領域の配線密度とメッシュ領域の各辺に隣接する周辺領域の各々における配線密度とを示すメッシュ情報を生成するメッシュ情報生成部12,各メッシュ領域について,メッシュ領域と各周辺領域の密度の関係がEOEの発生条件に該当するメッシュ領域を抽出し,そのエラー情報を生成するエラー抽出部13を備える。

(もっと読む)

半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラム

【課題】レイアウト設計において、複数のI/Oバッファセルを2列以上に配列する場合、I/Oバッファ領域の近傍にリピータを挿入する領域を確保し、手戻りをできるだけ抑えることができる、半導体集積回路設計支援装置、半導体集積回路設計方法およびプログラムを提供する。

【解決手段】リピータを含まないフィルセル(FC)と、リピータを含むフィルセル(FCR)とが用いられる。フィルセル(FC)は、同列で互いに隣接したI/Oバッファセル(Bm=1、n、Bm=1、n+1など)間に配置される。なお、複数のI/Oバッファセルは、2列に配置されている。I/Oバッファセルからプリミティブセルまでの配線長に基づいて、すでに配置されているフィルセル(FC)が、リピータを含むフィルセル(FCR)に置換される。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

81 - 90 / 3,836

[ Back to top ]