国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

121 - 130 / 3,836

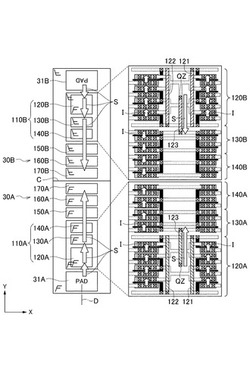

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

121 - 130 / 3,836

[ Back to top ]