国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

151 - 160 / 3,836

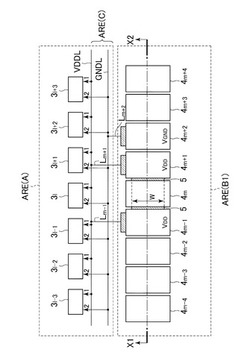

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

半導体集積回路装置

【課題】容易にカスタマイズ対応可能な半導体集積回路装置を提供する。

【解決手段】アレイ型プロセッサ部(300)は、プロセッサエレメント(330)とプログラマブルスイッチ(320)とを備えるプロセッサユニット(310)をマトリクス状に配置する。プロセッサエレメント(330)は、複数ビット幅の第1演算器(332)と複数ビット幅より狭い所定のビット幅の第2演算器(333)とを有する。第1演算器(332)および第2演算器(333)の接続構成は構成情報メモリ(340)に設定される構成情報に基づいて変更可能である。プログラマブルスイッチ(320)は、配線からプロセッサエレメントに複数ビット幅のデータおよび所定のビット幅のデータを構成情報に基づいて入出力する。制御回路(200)は、内部バス(180)に接続され、アレイ型プロセッサ部(300)の動作を制御し、内部バス(180)を介してデータを授受する。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップサイズ見積もり方法

【課題】精度よく簡便にチップサイズを見積もることができる、半導体集積回路のチップサイズ見積もり装置、及び半導体集積回路のチップ見積もり方法を提供する。

【解決手段】回路の機能の実現に最小限必要なゲート数である最小機能ゲート数を入力する入力部1と、セルライブラリごとに所定の動作速度の達成に必要となるゲート数と前記最小機能ゲート数との比率である性能考慮ゲート数係数が予め設定された設定値保持部21と、前記最小機能ゲート数と前記性能考慮ゲート数係数とから算出されるゲート数を用いて前記回路の総面積を見積もる計算部22と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路の配線設計検証方法

【課題】検証に要する時間をより短縮できる半導体集積回路の配線設計検証方法を提供する。

【解決手段】設計仕様(S7)に基づいてユーザが回路図(S8)に入力した各配線部の最大許容電流値Imaxと、電流密度Jと、配線膜厚hとを抽出し、これらに基づいて各配線部の最小配線幅情報Wmin(S12)を求める。またレイアウトのデータ(S1)から、各配線部に対応する配線経路の情報を付した配線経路ネットリスト(S4)と、各配線部について配線幅情報を付した配線幅ネットリスト(S6)とを作成し、配線経路ネットリストにおける各配線経路について各配線部の最小配線幅情報Wminを付したものと、配線幅ネットリストにおいて対応する配線部の配線幅情報とを比較して、各配線部に流れる電流が許容されている電流値以下か否かを検証する(S13)。

(もっと読む)

151 - 160 / 3,836

[ Back to top ]