国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

141 - 150 / 3,836

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

論理回路

【課題】電源電位の供給が遮断されたときでも論理回路の切り替え状態の保持が可能で、電源投入後の論理ブロックの起動時間が短く、低消費電力化が可能な、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる論理回路を提供する。

【解決手段】酸化物半導体を有するトランジスタを介して、ノードへの電荷保持状態を切り替えることによって、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる。当該トランジスタにはワイドバンドギャップ半導体である酸化物半導体材料を用いることによって、トランジスタのオフ電流を十分に小さくできるため、ノードに保持した電荷の状態を不揮発とすることができる。

(もっと読む)

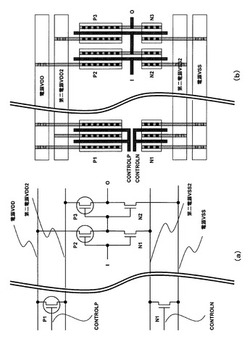

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

141 - 150 / 3,836

[ Back to top ]