国際特許分類[H01L21/82]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684)

国際特許分類[H01L21/82]の下位に属する分類

基板がシリコン技術を用いる半導体であるもの (27,844)

基板がIII−V技術を用いる半導体であるもの

基板がII−VI技術を用いる半導体であるもの

基板がグループ21/822,21/8252または21/8254の1つに包含されない技術を用いる半導体であるもの

基板が21/822,21/8252,21/8254または21/8256に包含される技術の組み合わせを用いる半導体であるもの

基板が半導体本外以外のもの,例.絶縁体本外のもの (4)

国際特許分類[H01L21/82]に分類される特許

101 - 110 / 3,836

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

配線抵抗網作成装置および配線抵抗網作成方法

【課題】配線形状の複雑化に起因するエレクトロマイグレーション解析の処理時間の増加を抑制する。

【解決手段】配線パターン分割部(22)と、ビア部分抵抗網設定部(25)と、配線部分抵抗網設定部(24)と、配線抵抗・ビア抵抗接続部(28)を有する配線抵抗網作成装置(10)を構成する。配線パターン分割部(22)は、レイアウトデータからビアとの接続位置情報を含む配線パターンを取得し、配線パターンをアレイビア部分と配線部分に分割する。ビア部分抵抗網設定部(25)は、アレイビア部分に対応するビアノードおよびビア部分抵抗を含むビア部分抵抗網を設定する。配線部分抵抗網設定部(24)は、配線部分に対応する配線ノードおよび配線部分抵抗を含む配線部分抵抗網を設定する。配線抵抗・ビア抵抗接続部(28)は、ビア部分抵抗網と配線部分抵抗網を接続して配線抵抗網データを生成する。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置設計方法および半導体装置設計支援プログラム

【課題】EBDに近いモデリング精度を維持しつつ、モデリングの効率を高める。

【解決手段】複数のチップ(CHIP1〜4)が積層され、それぞれのチップが共通の外部端子104に接続される積層型の半導体装置100の設計に関する。まず、電磁界解析ツールにより、外部端子104とチップを接続するプリント基板配線(共通配線106、個別配線108)の電気的なパラメータを算出し、それらをEBDのパラメータとして設定する。設定されたパラメータに基づいて半導体装置100の電気的な特性をシミュレーション計算する。パラメータの計算・設定に際しては、所定の配線、たとえば、共通配線106や個別配線108などのプリント基板配線の長さを示すパラメータをゼロに設定する。

(もっと読む)

ノイズ解析装置及びノイズ解析方法

【課題】半導体集積回路で発生するノイズの伝搬を精度よく解析する。

【解決手段】位置特定部2が、解析対象の半導体集積回路のレイアウト情報d1から、高耐圧素子部において、可変容量として設定する、異なる導電型の領域間の接合部の位置を特定し、モデル作成部3が、レイアウト情報d1及び半導体集積回路の製造条件(プロセスパラメータd2)をもとに、ノイズ伝搬路となる配線または基板を、抵抗及び容量を用いてモデル化し、特定された接合部の位置には可変容量を設定する。

(もっと読む)

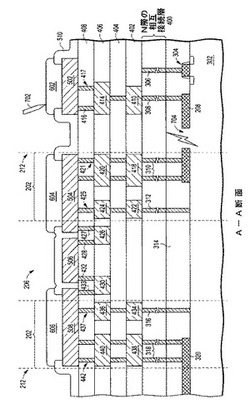

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

ネットリスト変換装置、論理合成装置及びコンピュータプログラム

【課題】半導体集積回路の開発期間を短縮し、且つ、レイアウトエラー確率を低減する。

【解決手段】本発明の実施形態のネットリスト変換装置は、半導体集積回路を構成する複数のセルであって、第1遅延時間だけスキャン用データ信号を遅延させる第1スキャンフリップフロップを含む複数のセルの接続関係を示すネットリストを変換する。そのようなネットリスト変換装置は、論理ライブラリ30と、ネットリスト変換部18と、を備える。論理ライブラリ30は、半導体集積回路を構成する複数のセルの論理的機能を示す情報を含むセル論理情報であって、第1スキャンフリップフロップの論理的機能を示す情報と、第1遅延時間より大きいスキャン用第2遅延時間だけデータ信号を遅延させる第2スキャンフリップフロップの論理的機能を示す情報と、を含むセル論理情報を記憶する。ネットリスト変換部18は、セル論理情報を参照して、ネットリストの第1スキャンフリップフロップを第2スキャンフリップフロップに置換する。

(もっと読む)

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

101 - 110 / 3,836

[ Back to top ]