国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

2,391 - 2,400 / 2,471

半導体記憶装置

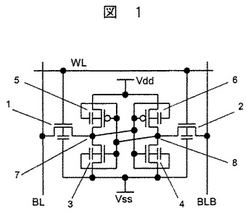

SRAMメモリセルをFD-SOIトランジスタで構成し、駆動トランジスタを構成するSOIトランジスタの埋め込み酸化膜の下の層の電位を制御して、メモリセルの性能を向上させる。

【課題】

低電源電圧状態でのSRAM回路の性能を向上させる。

【解決手段】

FD-SOIトランジスタを用いて構成されたSRAMメモリセルにおいて、駆動トランジスタのBOX層下のウエル電位を制御することでVthを制御して電流を増加させて、メモリセルの安定動作を可能とする。

(もっと読む)

半導体装置の製造方法

【課題】更なる微細化を促進できる半導体装置の製造方法を提供すること。

【解決手段】 第1の半導体層1上に、第1半導体層1よりも絶縁化し難い第2半導体層3を形成する工程と、第2半導体層3の上面から第1半導体層1にかけて、第2半導体層3、及び第1半導体層1を露出させる溝7を形成する工程と、溝7から露出する第1半導体層1、及び第2半導体層3を絶縁化し、溝を、絶縁化した第1半導体層9で閉じる工程とを具備する。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

メモリ・アレイ、メモリ・アレイを形成する方法、及びビット線に対するコンタクトを形成する方法

本発明は、メモリ・アレイと、メモリ・アレイを形成するために利用することができる方法を含む。ビット線コンタクト位置まで開口を残しながらストレージ・ノード・コンタクト位置を覆うパターン化されたエッチング停止層が、メモリ・アレイの製造期間に使用される。エッチング停止層上及びビット線コンタクト位置上に絶縁材料を形成し、絶縁材料を通ってトレンチが形成される。トレンチ内に導電材料を設け、ビット線コンタクト位置と電気的に接触し且つエッチング停止層によってストレージ・ノード・コンタクト位置から電気的に分離されたビット線相互接続線を形成する。後続の処理において、エッチング停止層を通って、ストレージ・ノード・コンタクト位置まで開口を形成する。次いで、開口内に、ストレージ・ノード・コンタクト位置と電気的に接触するようにメモリ記憶装置を形成する。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

半導体構成及び半導体構造の形成方法

本発明は、ケイ化物を含む埋込みビット線を有する半導体構造を含む。縦型SGT(サラウンド・ゲート・トランジスタ)構造がビット線の上に形成される。SGT構造は、DRAMデバイスなどのメモリ・デバイスに組み込むことができる。本発明は4F2DRAMデバイスの形成に利用することができる。  (もっと読む)

(もっと読む)

酸化ハフニウム層および酸窒化ハフニウム層または酸化ジルコニウム層および酸窒化ジルコニウム層のための前駆体としての溶解ハフニウムアルコキシドまたはジルコニウムアルコキシドの使用

本発明は、酸化ハフニウム層および酸窒化ハフニウム層用の前駆体としての高濃度の少なくとも1種のハフニウムアルコキシド溶液の使用に関するものである。本発明は特には、CVD法またはALD法用の酸化ハフニウム層および酸窒化ハフニウム層を製造するための濃度30〜90重量%の少なくとも1種のハフニウムアルコキシドの溶液の使用に関するものである。さらに本発明は、コーティング対象物上での酸化ハフニウム層および酸窒化ハフニウム層の製造方法、ならびに30〜90重量%の少なくとも1種のハフニウムアルコキシドを含むハフニウムアルコキシド溶液に関するものである。本発明の別の実施形態では、前記化合物において、ハフニウムをジルコニウムに置き換える。 (もっと読む)

半導体メモリセルおよびその製造方法

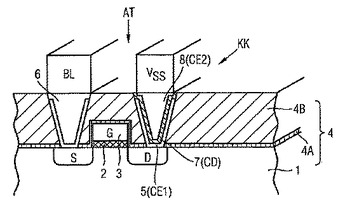

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

集積回路メモリーセル及びその製法

【課題】セルデザインや工程を不必要に複雑化せずにセルサイズを減少させる。

【解決手段】

チャンネル30は、組み合わされた第1電極と第1ソース/ドレーンの半導電性上方延長部を含むことができる。メモリーセルは複数のメモリーセルのアレイを含んでおり、第2電極は複数の電極の中の共通電極である。メモリーセルは、第1電極とデジット線との間に直線導電通路を提供することができ、その通路は垂直トランジスターを通過して延びている。

(もっと読む)

2,391 - 2,400 / 2,471

[ Back to top ]