国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

2,411 - 2,420 / 2,471

フラッシュ/ダイナミックランダムアクセスメモリフィールドプログラマブルゲートアレイ

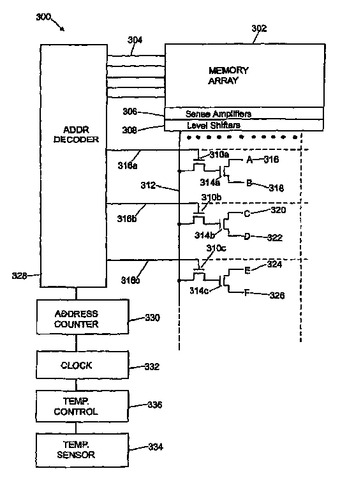

集積回路デバイスにおいて2つのノードを選択的に相互接続するための回路は、複数のワード線及び複数のビット線を有するメモリアレイを含む。リフレッシュトランジスタは複数のビット線のうち一本に接続されたソース、ダイナミックランダムアクセスメモリワード線に接続された制御ゲート、及びドレインを有する。スイッチトランジスタはリフレッシュトランジスタのドレインに接続されたゲート、一番目のノードに接続されたソース、及び二番目のノードに接続されたドレインを有する。アドレスデコーダはワード線とダイナミックランダムアクセスメモリワード線に周期信号を供給する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

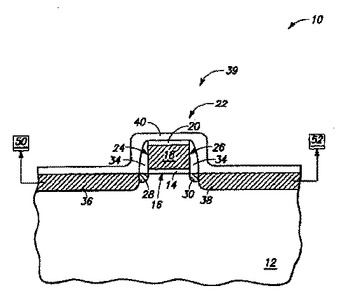

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

半導体メモリ素子及び該素子を動作させる方法

【課題】 行と列のマトリクスに配置された複数の半導体ダイナミック・ランダム・アクセス・メモリセルを含む半導体メモリアレイを提供する。

【解決手段】 第1の実施例では、本発明はメモリ素子とメモリ素子のメモリセルからデータを読み取る及びメモリセルにデータを書き込む技術を対象としている。この点において、本実施形態の本実施例の1つの実施形態では、メモリ素子及びその素子を動作させる技術は、電荷ポンピング現象の衰弱効果を最小限にする、削減する及び取り除く。本発明の本実施形態は、振幅及び/又は極性の遷移を最小限にする、削減する及び/又は取り除く制御信号を採用する。別の実施形態では、本発明は行と列のマトリクスに配置された複数の半導体ダイナミック・ランダム・アクセス・メモリを含むメモリアレイを含む半導体メモリ素子である。それぞれの半導体ダイナミック・ランダム・アクセス・メモリセルは、ソース領域、ドレイン領域、ソース領域とドレイン領域の間に及びそれらに隣接して配置される電気的浮体領域、及びそのボディ領域から離れ、及びそれと容量結合されたゲートを有するトランジスタを含む。それぞれのトランジスタは、ボディ領域の第1の電荷を表す第1の状態、及びボディ領域の第2の電荷を表す第2のデータ状態を含む。さらに、半導体ダイナミック・ランダム・アクセス・メモリセルのそれぞれの行は、関連する行の半導体ダイナミック・ランダム・アクセス・メモリセルだけに結合される関連するソース線を含む。

(もっと読む)

半導体メモリセル、アレイ、構造及び素子、及びこれらを動作させる方法

【課題】 第1のデータ状態と第2のデータ状態を保存する半導体ダイナミック・ランダム・アクセス・メモリセルを提供する。

【解決手段】 ここには、多くの発明が記載され及び示されている。第1の側面では、本発明はメモリセル及びメモリセルからデータを読み取る及びメモリセルへデータを書き込む技術を対象としている。これに関して、本発明の本側面の1つの実施形態では、メモリセルは相補的なデータ状態を保存する2つのトランジスタを含む。つまり、2つのトランジスタを持つメモリセルは、第2のトランジスタに対する相補的な状態を維持する第1のトランジスタを含む。そのため、プログラムされるとき、メモリセルのトランジスタの1つが論理低(バイナリ「0」)を保存し、及びメモリセルの他のトランジスタが論理高(バイナリ「1」)を保存する。2つのトランジスタを持つ相補的なメモリセルのデータ状態は、相補的なメモリセルの各トランジスタに保存された論理状態の極性をサンプリングする、検出する、測定する及び/又は検知することにより読み取られる及び/又は決定される。つまり、2つのトランジスタを持つ相補的なメモリセルは、2つのトランジスタに保存される信号(電流又は電圧)の差異をサンプリングする、検出する、測定する及び/又は検知することにより読み取られる。

(もっと読む)

トリス(オクタン−2,4−ジオナト)イリジウム、これを含有してなる化学気相成長用原料及び薄膜の製造方法

【課題】 CVD法に適する液体イリジウム化合物、これを用いたCVD用原料、及び該CVD用原料を用いたイリジウム薄膜の製造方法を提供すること。

【解決手段】 トリス(オクタン−2,4−ジオナト)イリジウム。

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

半導体装置

【課題】 消費電力が小さく、かつ動作速度が速い半導体装置を提供する。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

2,411 - 2,420 / 2,471

[ Back to top ]