国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

2,401 - 2,410 / 2,471

容器コンデンサ及び作製方法

【課題】半導体構造体、及び複数のコンデンサ装置の作製方法を提供する。

【解決手段】本発明の例示的方法においては、絶縁材(28)中の開口部内に導電性蓄積ノード部材(60)が形成されて導電性容器が作製される。保持構造体(30)が容器の少なくとも一部と物理的接触状態となるように形成され、次いで絶縁材(28)が除去されることにより容器の外側表面が露出される。保持構造体(30)によって容器構造体のぐらつきあるいは他の構造上の欠陥が減じられる。導電性容器は第一コンデンサ電極に相当する。容器の外側側壁が露出された後、絶縁材(100)が容器内に露出された外側側壁に沿って形成される。その後に第二コンデンサ電極(103)が絶縁材上へ形成される。これら第一及び第二コンデンサ電極と絶縁材とによって複数のコンデンサ装置が作製される。

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

半導体集積回路装置

記憶回路STCと比較回路CPとを用いたメモリセルで構成されるメモリアレイにおいて、比較回路CPを構成する複数のトランジスタのうち、ゲート電極がサーチ線に接続されるトランジスタのソースまたはドレインのいずれか一方の電極を高電圧にプリチャージされる方のマッチ線HMLrに接続する。また、マッチ線判定回路MDrを低電圧にプリチャージされるマッチ線LMLrに配置して、情報の比較結果に応じてこのマッチ線に発生した比較信号電圧を弁別する。このようなメモリアレイ構成と動作により、マッチ線対におけるサーチ線駆動雑音の影響を回避しつつ、低電力かつ高速に比較動作を行うことができる。このため、検索動作を高速に行うことが可能な低電力コンテント・アドレッサブル・メモリを実現することができる。 (もっと読む)

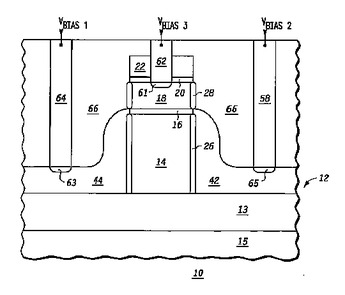

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

ハフニウムベースの高誘電率誘電体の原子層堆積

ハフニウムベースの誘電体膜を堆積する方法が提供される。本方法は、オゾンとハフニウム前駆体を含む1つ又はそれ以上の反応物質とを用いた原子層堆積段階を含む。半導体デバイスもまた提供される。該デバイスは、基板と、基板上に形成されたハフニウムベースの誘電体層と、基板及びハフニウムベースの誘電体層間に形成された界面層とを含み、該界面層は二酸化ケイ素を含み且つ結晶構造を有する。 (もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

コンデンサ構造体、でこぼこ状珪素含有面、及びでこぼこ状珪素含有面形成方法

【課題】でこぼこ状珪素含有面の形成方法を提供する。

【解決手段】 非晶質珪素が含まれた層を第一温度に設定された反応室内へ供する。水素同位元素の少なくとも1種を反応室中へ流入させながら、温度を前記第一温度よりも少なくとも40℃高い第二温度まで上昇させる。温度が第二温度まで達したら、前記層へ種子結晶を加える。次いで種子結晶が加えられた層をアニール処理してでこぼこ状珪素含有面を形成させる。でこぼこ状珪素含有面はコンデンサ構造体へ組み入れることができる。このようなコンデンサ構造体をDRAMセル中へ組み入れ、組み入れられたDRAMセルは電子装置に利用可能である。

(もっと読む)

半導体装置作製における垂直向きコンデンサ用支持体

半導体装置に用いる両面コンデンサの作製方法であって、該方法は、ウェハー加工間、コンデンサ底板(110)を支持する絶縁体構造体(86)を形成する工程を含む。前記構造体は、底板外側を露出させて両面コンデンサを作製するため底部絶縁体層(84)の除去中底板を支える点において特に有用である。支持構造体によって、セル誘電体層(200)、コンデンサ上板(202)及び最終絶縁体(204)の作製中も底板が支持される。また本発明による構造体についても開示されている。

(もっと読む)

(もっと読む)

垂直型トレンチ・トランジスタの形成方法(垂直パス型トランジスタDRAMセルの設計におけるデバイス縮小化のための自己整合型ドレイン/チャネル接合)

【課題】 改善されたしきい値のばらつきをもたらし、従来技術に存在するデバイスより優れたチャネル長の拡張容易性を提供する、垂直型金属酸化物半導体電界効果トランジスタ(MOSFET)を製造すること。

【解決手段】 垂直型ディープトレンチ・トランジスタを形成する方法が提供される。ドープされた半導体基板内に側壁を有するディープトレンチが形成される。半導体基板は、カウンタードープされたドレイン領域をその表面内に含み、側壁に並んだチャネルを含む。ドレイン領域は上部レベル及び下部レベルを有する。カウンタードープされたソース領域がチャネルの下方の側壁と並置された基板内に形成される。ゲート酸化物層が、ゲート導体と並置されたトレンチの側壁上に形成される。ドレイン領域の下部レベルの下方にゲート導体を陥凹させるステップに続いて、垂直線に対して角度θ+δで、ソース領域より下方のチャネル内にカウンタードーパントの傾斜イオン注入を行うステップと、垂直線に対して角度θで、ソース領域の下方のチャネル内にドーパントの傾斜イオン注入を行うステップとを行う。

(もっと読む)

2,401 - 2,410 / 2,471

[ Back to top ]