国際特許分類[H01L25/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器をもつ装置 (1,024)

国際特許分類[H01L25/10]の下位に属する分類

装置がグループ29/00に分類された型からなるもの (496)

装置がグループ33/00に分類された型からなるもの

国際特許分類[H01L25/10]に分類される特許

11 - 20 / 528

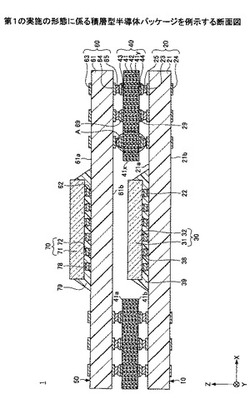

積層型半導体パッケージ

【課題】高密度に相互接続した積層型半導体パッケージを提供する。

【解決手段】第1の配線基板20に第1の半導体チップ30が実装され、一方の側に第1の電極パッド23が形成された第1の半導体パッケージ10と、第2の配線基板60の他方の側に第2の電極パッド64が形成された第2の半導体パッケージ50は、半導体チップ収容孔41xと、絶縁性基材41を厚さ方向に貫通する複数の線状導体42に接合された第3の電極パッド42と、第4の電極パッド44と、を備えた接続用部材40で接合される。

(もっと読む)

半導体パッケージの製造方法及び半導体パッケージ

【課題】絶縁部材の充填不良を低減すること。

【解決手段】支持板44の突起部43が形成された面には、回路基板接続用パッド31と、実装用パッド16と、回路基板接続用パッド31及び実装用パッド16を接続する接続部(層間接続部32及び配線部33)がめっきにより形成される。支持板44は、半導体チップ14が実装された回路基板40に対向配置され、回路基板接続用パッド31がバンプ20を介して内部接続用パッド19に接続される。回路基板40と支持板44との間には、樹脂が充填され絶縁層15が形成される。支持板44は、エッチングにより除去される。

(もっと読む)

半導体装置および半導体装置ユニット

【課題】半導体パッケージをより小型とすることができる半導体装置を提供すること。

【解決手段】回路素子の少なくとも一部が形成された半導体基板3と、半導体基板3の表面に配置された1または複数の表面電極41a,41bと、半導体基板3の裏面に配置され、上記回路素子と導通している裏面電極42と、を備え、表面電極41a,41bが上記回路素子と導通している、半導体装置A1であって、上記表面の側に配置されており、かつ、半導体基板3、表面電極41a,41bおよび裏面電極42を支持している支持基板1と、表面電極41a,41bと導通しているとともに半導体基板3を貫通している導電部51a,51bと、をさらに備える。

(もっと読む)

複合型積層チップパッケージ

【課題】サブパッケージ内の1つ以上の半導体チップに対応付けられる複数の信号のうちのいくつかを、サブパッケージ毎に容易に変える。

【解決手段】複合型積層チップパッケージ21は、積層された第1および第2のサブパッケージ1Sを備えている。各サブパッケージ1Sは本体と配線を備えている。本体は、主要部分の上面に配置された複数の第1の端子と、主要部分の下面に配置された複数の第2の端子を有している。第1および第2のサブパッケージ1Sは、基準の相対的位置関係とは異なる特定の相対的位置関係で配置されている。いずれの相対的位置関係においても、互いに接する第1のサブパッケージ1Sにおける第1の端子と第2のサブパッケージ1Sにおける第2の端子の複数の対が形成される。特定の相対的位置関係では、対を構成する第1の端子と第2の端子の組み合わせが、基準の相対的位置関係とは異なる。

(もっと読む)

半導体装置及びプリント回路板

【課題】第1インターポーザの一方の面に配列された複数の第1ボール電極による接合信頼性が高い小型の半導体装置を提供する。

【解決手段】第2インターポーザ233の第1インターポーザ213と対向する面233aにおいて、一方向に延びる複数の第1直線と、該第1直線と異なる方向に延びる複数の第2直線とが交差する格子点に第2ボール電極235が配置されている。その際、第2インターポーザ233の角部に最も近い角部格子点を、第1及び第2インターポーザ213,233を非接合状態とする非接合格子点とした。

(もっと読む)

エッジ接続ウエハレベル積層体

【課題】ウエハレベルで製造される積層超小型電子パッケージ、およびこのようなパッケージを製造する方法を提供する。

【解決手段】複数の超小型電子素子を備える第1のサブアセンブリ210を複数の超小型電子素子を備える第2のサブアセンブリ210上に積層した積層アセンブリ280は、それらのエッジに延在するトレース(配線)を有し、次いで、トレースを露出させるために、超小型電子アセンブリ内に部分的にノッチを形成し、続いて、アセンブリの平坦な面に電気接点の端2668をもたらすために、ノッチの側壁にリード2666を形成する。

(もっと読む)

半導体装置、半導体パッケージ、半導体装置の製造方法及び半導体パッケージの製造方法

【課題】電気的接続信頼性を向上させることができる半導体装置を提供する。

【解決手段】半導体チップ3は、第1主面30Aと第2主面30Bとの間を貫通する貫通孔30Xを有する半導体基板30と、半導体基板30の第2主面30Bを覆うように形成され、貫通孔30Xと対向する位置に開口部31Xが形成された絶縁層31と、絶縁膜33によって覆われた貫通孔30X及び開口部31Xに形成された貫通電極32とを有する。絶縁層31から露出される貫通電極32の上端面は、当該半導体チップ3に他の半導体チップ4が積層される際のパッドになる。また、貫通電極32の上端面は、絶縁層31の半導体基板30と接する面と反対側の面と面一になるように形成されている。

(もっと読む)

半導体パッケージ

【課題】系統毎の配線長の違いを抑制し、高速動作を実現できる半導体パッケージを提供すること。

【解決手段】第1主面と、第1主面に対向した第2主面とを有する矩形の基板と、第1主面上に実装される第1の半導体チップと、第1の半導体チップ上に積層される1以上の第2の半導体チップと、1以上の第2の半導体チップ上に積層される1以上の第3の半導体チップと、を備え、基板は、第1主面上の第1の辺側に、1以上の第2の半導体チップの電極と接続される第1の接続端子と、第1の接続端子と電気的に接続され、第1の半導体チップの第1の電極と接続される第3の接続端子と、を有し、第1主面上の第1の半導体チップを挟んで第1の辺と対向する第2の辺側に、1以上の第3の半導体チップの第2の電極と接続される第2の接続端子と、第2の接続端子と電気的に接続され、第1の半導体チップの電極と接続される第4の接続端子と、を有する。

(もっと読む)

パッケージ積層構造物

【課題】 非対称の伝導性構成要素を有するパッケージ積層構造物を提供する。

【解決手段】 パッケージ積層構造物は、第1辺S1、第1辺S1と対向する第2辺S2、第1辺に近い第1領域及び第2辺S2に近い第2領域を含む上部パッケージ基板901cと、上部パッケージ基板901c上に配置された第1上部半導体素子を含む上部パッケージ900cと、下部パッケージ基板606c及び下部半導体素子650を有し、複数のパッケージ間接続部990A、990Bを介して上部パッケージに接続される下部パッケージと、を有する。パッケージ間接続部990A、990Bは、第1パッケージ間接続部、第2パッケージ間接続部、第3パッケージ間接続部、および第4パッケージ間接続部を有する。第1パッケージ間接続部及び第2パッケージ間接続部は第1領域内に配置され、第3パッケージ間接続部は第2領域内に配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】ミドルサイド電極の界面について、封止樹脂との接合やはんだ接合の状態を正確に検査することができる半導体装置及びその製造方法を提供する。

【解決手段】第1の半導体素子10を両面から挟むように、ローサイド電極40及び第1のミドルサイド電極50が設けられ、ローサイド電極40及び第1のミドルサイド電極50の外側の面が露出するように封止樹脂100によりモールド成形された第1の樹脂モールド110と、第2の半導体素子11を両面から挟むように、ハイサイド電極60及び第2のミドルサイド電極51が設けられ、ハイサイド電極60及び第2のミドルサイド電極51の外側の面が露出するように封止樹脂によりモールド成形された第2の樹脂モールド120とを有し、第1のミドルサイド電極50と第2のミドルサイド電極51の外側の面同士が、接合又は圧接により一体的に固定されるとともに、電気的に接続されている。

(もっと読む)

11 - 20 / 528

[ Back to top ]