国際特許分類[H01L27/08]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288)

国際特許分類[H01L27/08]の下位に属する分類

バイポーラ構成部品のみを含むもの (131)

電界効果構成部品のみを含むもの (6,291)

国際特許分類[H01L27/08]に分類される特許

101 - 110 / 1,866

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜に劣化が生じることを抑制する。

【解決手段】ハードマスクを用いて素子分離溝102を形成した後、素子分離溝102に素子分離膜20を埋め込む。次いで、ハードマスクの窒化シリコン膜210を除去する。次いで、ハードマスクの表面酸化膜200を薄くする。その後、シリコン基板100を熱酸化することにより、表面酸化膜を厚くして再酸化膜202を形成する。次いで、第1素子形成領域101及び第2素子形成領域103に位置するシリコン基板に、再酸化膜202を介してチャネル不純物を注入する。次いで、再酸化膜202を除去する。次いで、第1素子形成領域101に位置するシリコン基板100に、ゲート絶縁膜110及びゲート電極120を形成する。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

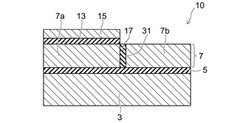

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

101 - 110 / 1,866

[ Back to top ]