国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

1,071 - 1,080 / 3,785

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体メモリ装置

【課題】 非選択セルに流れる逆方向バイアスの電流を低減することができ、かつ降伏現象への耐圧を増加し高電位でも対応可能な、ReRAMセルから構成されたメモリセルアレイを有する半導体メモリ装置を提供することを目的とする。

【解決手段】 本発明の実施形態による半導体メモリ装置におけるReRAMセルMは、ビット線BLとワード線WLとの交差部かつ間に、それらビット線BLとワード線WLとに電気的に接続されるように形成されている。そして、ReRAMセルMは、第1電極1、第1ダイオードD1、抵抗素子R、第2ダイオードD2、第2電極2の順番に、ビット線BLからワード線WL方向にそれらが直列的に接続されて形成されている。

(もっと読む)

半導体装置の製造方法

【課題】膜厚が薄く充分な不純物濃度を有する不純物領域を備えるダイオードを有する半導体装置の製造方法を提供する。

【解決手段】アモルファスシリコン層105を形成する工程と、シリコン層105上にガスを用いて不純物層106を吸着させる工程と、不純物層106上にアモルファスシリコン層107を形成する工程と、シリコン層107上に他のガスを用いて不純物層108を吸着させる工程と、不純物層108上にアモルファスシリコン層109を形成する工程と、シリコン層109上に下部電極層15を形成する工程と、下部電極層上に可変抵抗層11を形成する工程と、可変抵抗層上に上部電極層16を形成する工程と、上部電極層、可変抵抗層、下部電極層、シリコン層109、不純物層108、シリコン層107、不純物層106、及びシリコン層105をパターニングして柱状構造を形成する工程と、シリコン層109の形成後に熱を加える工程とを含む。

(もっと読む)

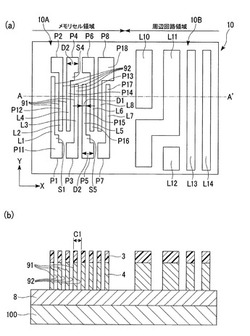

半導体集積回路装置

【課題】メモリマクロを含む半導体集積回路装置の遅延故障を確実に検出できないという問題があった。

【解決手段】メモリマクロを備える半導体集積回路装置1であり、スキャンモード制御信号(SMC)に応じて、入力データ信号の値とスキャンテスト値とのいずれかを、動作クロックに従って保持する入力データ保持部22−0〜22−kと、テストモード制御信号(TEN)に応じて、入力データ保持部22−0〜22−kが保持する値とメモリセル部が記憶するデータ値とのいずれかを、複数の入力データ保持部が動作する位相とは異なる位相に従って保持する出力データ保持部41−0〜41−kと、を備える。入力データ保持部22−0〜22−kと、出力データ保持部41−0〜41−kとは、入力データ保持部22−0を先端として交互に直列に接続され、複数の出力データ保持部の一つが保持する値は、スキャンテスト値として後段の入力データ保持部へ伝送される。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】抵抗変化層と整流層とを含む積層膜を柱状のメモリセルを加工する場合に、パターン倒れやメモリセル下部での隣接するメモリセルとの間のパターンショートの発生を抑える不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の配線11が形成された第1の層間絶縁膜10上に、整流層21および抵抗変化層22を含む積層体と絶縁膜24とを形成し、メモリセル形成位置が開口したパターンを第1の配線11の形成位置上に二次元的に配置したレジストパターンを形成し、レジストパターンを用いて、絶縁膜24をエッチングして開口部を形成し、開口部内に導電性材料膜を埋め込んでマスク膜23を形成し、マスク膜23をマスクとしてドライエッチング法によって絶縁膜24、整流層21および抵抗変化層22をエッチングしてメモリセルを形成し、メモリセル間に第2の層間絶縁膜を埋め込み、メモリセルの上面と接するように第2の配線を形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】高さ方向に隣接するメモリセル間でワード線またはビット線を共有する構造の不揮発性記憶装置に設けられるコンタクトを形成するための工程数を従来に比して削減することができる不揮発性記憶装置を提供する。

【解決手段】第2の層間絶縁膜30上のメモリセル形成領域RM上には、異なる高さに形成され互いに方向が異なるビット線BLとワード線WLの交差位置にマトリックス状に配置された抵抗変化型メモリセルを含むメモリ層が高さ方向に複数積層されたメモリセル部100が形成され、コンタクト形成領域RC上には、第2の配線35と層間絶縁膜60上に形成された第3の配線91とを接続するコンタクトWC,BCが形成され、コンタクトWC,BCは、各メモリ層に対応して形成される同じ開口径のコンタクト形成用溝が深さ方向に連続して接続されるコンタクトホールに導電性材料が埋め込まれる構造を有する。

(もっと読む)

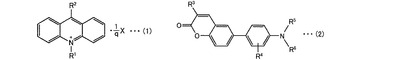

光照射によって誘電率が変化する膜およびそれを用いた電子デバイス

【課題】光照射によって誘電率を変化させることが可能な膜、およびそれを用いた電子デバイスを提供する。

【解決手段】薄膜トランジスタ20は、ガラス基板21、ゲート電極22、ゲート絶縁膜23、半導体層(活性層)24、ソース電極25およびドレイン電極26を備える。ゲート電極22、ゲート絶縁膜23および半導体層24は、この順序でガラス基板21上に積層されている。ソース電極25およびドレイン電極26は、半導体層24上に形成されている。ゲート絶縁膜23は、有機重合体と、その有機重合体中に分散された化合物とを含む溶液を、ガラス基板上に形成されたゲート絶縁膜上にスピンコート法によって塗布した。その化合物は、以下の式(1)で表される化合物および以下の(2)で表される化合物から選ばれる少なくとも1種の化合物である。[化学式(1)および(2)] (もっと読む)

(もっと読む)

半導体記憶装置

【課題】不良セルによるリーク電流の伝播を抑制可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、直列接続された抵抗変化膜およびダイオードを含んだメモリセル(MC)を含む。メモリセルアレイ(MCA)は、第1、第2軸からなる直交座標面の各座標に配置されたメモリセルからなり、外周に沿った第1領域(DCA)および第1領域の外周と反対側に位置する第2領域(MCA)を有する。第1配線(BL)は、第1軸に沿ってメモリセルアレイの両端に亘って連続的に形成され、一部が第2領域内に位置し、複数のメモリセルの第1端と接続されている。第2配線(DBL)は、第1軸に沿い、第1配線と同じ膜に由来し、第1領域内のみに位置し、複数のメモリセルの第1端と接続され、隣接するメモリセル同士の間で分断されている。第3配線(WL)は、第2軸に沿ってメモリセルアレイの両端に亘って連続的に形成され、複数のメモリセルの第2端と接続されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】キャパシタ素子の配置面積低減が可能な半導体記憶装置を提供する。

【解決手段】メモリセル領域5及び周辺回路領域6を複数の素子形成領域に分離し、半導体基板11表面より上に上面を有する素子分離絶縁膜17と、メモリセル領域5の素子領域7上に、順に、トンネル絶縁膜13a、第1下層電極層15a、第1電極間絶縁膜19a、及び第1上層電極層25aとを有するメモリセル及び選択ゲートトランジスタ41、43と、周辺回路領域6の素子形成領域上に、上端に凹部18が加工された第2下層電極層15b、この凹凸面及び素子分離絶縁膜17上に配設され、第1電極間絶縁膜19aと同じ膜厚の第2電極間絶縁膜19b、及び第2電極間絶縁膜19b上に第2下層電極層15bに対応した凹凸の下面の第2上層電極層25bを有し、凹部18の底面が第1下層電極層15aの上面と同じ高さであるキャパシタ素子45とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線引き出し部を活性領域の上に形成する構成としながら、リーク電流を抑制する。

【解決手段】側壁転写プロセスで形成されたワード線をワード線引き出し部WLaでループカットすると共に、ワード線引き出し部WLaを半導体基板2の活性領域Sa上に配設する構成であって、電極間絶縁膜4に選択ゲートトランジスタ用開口4aを形成する際にワード線引き出し部形成領域にループカット用開口4bを形成しておき、電極間絶縁膜4およびゲート絶縁膜3に対して選択的にエッチングを行うことによりワード線引き出し部の上層電極および下層電極を連続的に分離しループカットできるようにした。

(もっと読む)

1,071 - 1,080 / 3,785

[ Back to top ]