国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

971 - 980 / 3,785

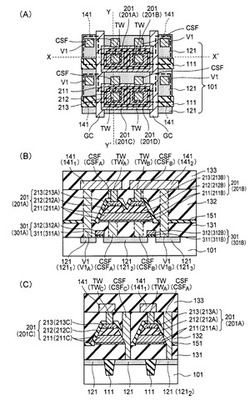

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 低コストで、生産性及び歩留まりに優れる構造の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

基板上の第1の金属配線119上に第1の開口部128を、第2の金属配線121上に第2の開口部129を同時に形成する。次に導電膜120を全面に堆積すると、開口面積の小さな第1の開口部内において、堆積される導電膜の膜厚に不均一が生じ、第1の開口部の底部と側壁部の境界部分に、膜厚が薄く堆積される局所薄膜領域が生じる。当該局所薄膜領域の導電膜が完全に酸化されるが、底部及び側壁部上には未酸化の導電膜が残存するような膜厚で導電膜を酸化させることにより、第1の開口部128内において、底部の導電膜122と側壁部の導電膜126が導電膜の酸化膜である可変抵抗体を介して分離され、可変抵抗素子104が形成される。一方、第2の開口部内には導電膜と第2の金属配線を接続するコンタクトが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能と製造歩留まりを向上させる。

【解決手段】半導体基板1の上部に、制御ゲート電極CGとその上の絶縁膜5とその上の絶縁膜6とを有する積層パターン7が形成され、半導体基板1の上部に、積層パターン7と隣り合うメモリゲート電極MGが形成されている。制御ゲート電極CGと半導体基板1との間にはゲート絶縁膜用の絶縁膜3が形成され、メモリゲート電極MGと半導体基板1との間および積層パターン7とメモリゲート電極MGとの間には、酸化シリコン膜9a、窒化シリコン膜9bおよび酸化シリコン膜9cの積層膜からなる絶縁膜9が形成されている。積層パターン7のメモリゲート電極MGに隣接する側の側壁では、絶縁膜5が制御ゲート電極CGおよび絶縁膜6よりも後退しており、制御ゲート電極CGの上端角部C1が丸みを帯びている。

(もっと読む)

改良型eDRAMアーキテクチャ

eDRAMデバイス(300)の製造方法は、DRAM領域(301)及びロジック領域(302)を含む半導体基板上に複数の半導体素子(304a〜e)を形成することを備える。また、本方法は、DRAM領域及びロジック領域内に、第一のグループの半導体素子と連通する第一の導電層(M1)を形成することも含む。第一の導電層を形成した後に、ストレージデバイス(312、313)が、DRAM領域内の第二のグループの半導体素子と連通して形成される。  (もっと読む)

(もっと読む)

強誘電体メモリ装置及びその製造方法

【課題】強誘電体膜の結晶化のための焼き締めによる熱処理不足によるメモリ特性の低下、特に強誘電体膜の残留分極特性の低下を防止しながら、製造プロセスの低温熱処理化を実現できる強誘電体メモリ装置を提供する。

【解決手段】強誘電体メモリ装置は、p型半導体基板1上に、下部電極10、ペロブスカイト型結晶構造を持つ強誘電体膜からなる容量絶縁膜11及び上部電極12がこの順に積層して形成された強誘電体キャパシタを備えている。上部電極12上に形成され、集光により強誘電体膜12を選択的に加熱する凸型レンズ14をさらに備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高速なアクセスが可能で、かつ、高集積化が可能なスプリットゲート型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板101の主表面の溝に第1、第2のスプリット型不揮発性メモリセルを形成した不揮発性半導体記憶装置100であって、溝内部の対向する第1、第2の側壁102a,102bの表面にそれぞれ第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とが形成され、第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とには、それぞれ異なる電圧を印加することが可能である。

(もっと読む)

不揮発性半導体メモリデバイス

【課題】ダイナミック放電読み出しでセンスタイミングのずれを是正する。

【解決手段】センスアンプ7Bは、メモリセル抵抗Rcellの一方の電極が接続されたビット線BLの放電電位を参照電位Vrと比較して情報を読み出す。セット容量スイッチ18S、リセット容量スイッチ18Rおよび追加容量Coffsetとその制御手段によって、センスノード(電位Vo)の負荷容量、または、センスノードと参照電位Vrを入力する参照ノードの負荷容量との両方を、メモリセル抵抗Rcellの読み出す情報の論理(通常読み出し、書き込みまたは消去のヴェリファイ読み出しの相違)に応じて変化させる。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルトランジスタの特性が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】ボロンドープドシリコン層72を堆積させ、その上面にシリコン窒化層78を形成し、ノンドープドシリコン層73を堆積させ、その上面にシリコン窒化層79を形成する工程を繰り返すことにより、シリコン基板11上に積層体20を形成する。次に、積層体20に貫通ホール30aを形成し、その内部に犠牲材を埋め込み、積層体20にX方向に延びるスリット74を形成する。次に、スリット74内にエッチング水溶液を導入することにより、ノンドープドシリコン層73をウェットエッチングして除去する。次に、エッチング水溶液を除去し、ボロンドープドシリコン層72間及びスリット74内に絶縁材料を埋め込む。次に、貫通ホール内から犠牲材を除去し、内面上に電荷蓄積膜を形成し、内部にシリコンピラーを形成する。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

971 - 980 / 3,785

[ Back to top ]