国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

991 - 1,000 / 3,785

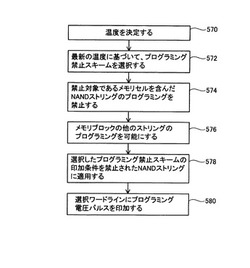

不揮発性メモリのプログラミング禁止スキームの選択的な使用

【課題】不揮発性メモリシステムを、プログラム妨害を低減又は防止するようにプログラムする。

【解決手段】1つの不揮発性メモリシステムに、複数のプログラム禁止スキームを採用している。プログラム禁止スキームは、プログラミング中のワードラインに基づいて選択される。特定のプログラム禁止スキームは、選択ワードラインにおいてプログラム妨害を好適に最小化又は排除する。プログラミング動作の前と最中に、メモリシステムの温度を検出する。プログラム禁止スキームは、システムの温度に基づいて選択できる。

(もっと読む)

無線通信機能を有する半導体装置

【課題】無線通信機能を有する半導体装置の低消費電力化、通信距離の拡大を図る。

【解決手段】メモリ部と、論理部と、メモリ部及び論理部間を電気的に接続する複数の信号線と、を備え、半導体装置及び通信装置間の転送レートをα[bps]、論理部で生成される第1のクロック周波数をKα[Hz](Kは1以上の整数)、複数の信号線のうち読み出し用信号線をn本(nは2以上の整数)、論理部で生成される第2のクロック周波数をLα/n[Hz](Lは、L/n<Kを満たす任意の整数)とした場合、メモリ部に格納されたデータを論理部へ読み出す場合は、第2のクロック周波数Lα/n[Hz]を用いて、n本の読み出し用信号線を介して行う。

(もっと読む)

半導体装置

【課題】従来のメモリ素子とは異なり、軟化又は溶融といった状態変化を利用したメモリ素子を提供し、メモリ容量が増大されたメモリ装置を提供することを課題とする。

【解決手段】一対の電極間に、ガラス転移温度が異なる複数のメモリ材料層を積層させたメモリ素子である。ガラス転移温度は10℃以上の差があると好ましい。このようなメモリ素子に電圧を印加することで、複数のメモリ材料層を一つずつ軟化又は溶融させる。このような構成により、メモリ容量が3値以上となり増大される。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】低電圧での情報書き込みと高密度集積とを両立し得る半導体記憶装置とその製造方法を提供すること。

【解決手段】本発明は、状態記憶素子31及びトランジスタ32を備える。状態記憶素子31は、第1の導電領域41、第1の絶縁膜43及び第1の電極45が半導体基板1上に順に形成されている。第2の絶縁膜44及び第2の電極46が半導体基板1上に順に形成されている。トランジスタ32は、第1の導電領域41、第2の導電領域42、第2の絶縁膜44、第2の電極46を有する。第2の絶縁膜44及び第2の電極46は、第1の導電領域41と第2の導電領域42との間の半導体基板1上に順に形成されている。また、第1の絶縁膜43の絶縁破壊耐圧は、第2の絶縁膜44の絶縁破壊耐圧よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み動作と消去動作との干渉を防止し、誤書き込みの発生を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、互いに交差する複数の第1及び第2の配線の各交差部に設けられ同一極性の電圧印加によってデータの書き込みと消去を行う複数のメモリセルからなるメモリセルアレイと、選択された第1及び第2の配線を介してメモリセルに対してセットパルス/リセットパルスを供給する書き込み回路とを備え、リセットパルスの電圧の大きさ及び電圧印加時間の組み合わせの集合であるリセット領域は、電圧の大きさ及び電圧印加時間の関係が負の相関関係を持つ領域であり、書き込み回路は、消去動作時、リセットパルスを、その電圧の大きさ及び電圧印加時間をリセット領域の範囲内で増減させながら、選択メモリセルに対してデータが消去されるまで繰り返し供給する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】回路構成を複雑化することなくソフトエラー低減化を図ったメモリセル構造を有する半導体記憶装置を得る。

【解決手段】NMOSトランジスタN1及びPMOSトランジスタP1によるインバータI1(出力部が記憶端子Na)とNMOSトランジスタN2及びPMOSトランジスタP2によるインバータI2(出力部が記憶端子Nb)とが交叉接続され、さらにNMOSトランジスタN3及びN4が記憶端子Na及びNbにそれぞれ接続される。記憶端子Naに一方電極が接続されるNMOSトランジスタN1及びN3はPウエル領域PW0及びPW1に分けて形成されるともに、記憶端子Nbに一方電極が接続されるNMOSトランジスタN2及びN4はPウエル領域PW1及びPW0に分けて形成される。Pウエル領域PW0及びPW1はNウエル領域NWを挟んで各々反対側に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

金属ナノ粒子を有する抵抗変化メモリ

【課題】抵抗変化メモリ素子の抵抗値のばらつきがなく、動作電圧の制御が可能な抵抗変化メモリ素子を提供する。

【解決手段】第1電極100と、第1電極100上に形成された遷移金属酸化物の抵抗変化層110と、抵抗変化層110上に形成された第2電極130、及び抵抗変化層110内に形成される金属ナノ粒子120を含む抵抗変化メモリ素子であって、フィラメント電流経路140は第2電極130と金属ナノ粒子120間でのみ形成される。これにより、メモリ素子の抵抗値を安定化することができる。

(もっと読む)

半導体装置の駆動方法

【課題】電荷蓄積層での電子の蓄積または放出が十分でない場合に、不揮発性メモリ素子に保持された記憶状態の正誤を判定し、誤ったデータを読み出すことによる不良を低減する。

【解決手段】メモリセル領域104と、テスト領域105と、を含む半導体記憶回路103と、制御回路と、を有し、制御回路は、メモリセルへのデータの書き込み、第1の領域105Aへの第1の記憶状態の書き込み、または第2の領域105Bへの第2の記憶状態の書き込みを行うための第1の動作を行い、第1の領域及び第2の領域からの第1の記憶状態または第2の記憶状態の読み出しを行うための第2の動作を行い、メモリセルからのデータの読み出しを行うための第3の動作を行い、第2の動作において、第1の領域からの読み出しが第1の記憶状態であるか、または第2の領域からの読み出しが第2の記憶状態であるかに応じて、第3の動作の正誤を判定する。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

991 - 1,000 / 3,785

[ Back to top ]