国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

1,021 - 1,030 / 3,785

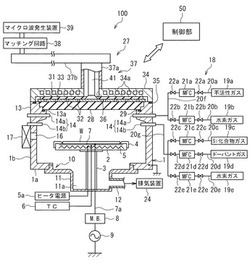

結晶性珪素膜の成膜方法およびプラズマCVD装置

【課題】 プラズマCVD法により良質な結晶性珪素膜を高い成膜レートで成膜する方法を提供する。

【解決手段】 複数の孔を有する平面アンテナにより処理容器内にマイクロ波を導入してプラズマを生成するプラズマCVD装置を用い、式SinH2n+2(ここで、nは2以上の数を意味する)で表される珪素化合物を含む成膜ガスを前記マイクロ波により励起してプラズマを生成させ、該プラズマを用いてプラズマCVDを行うことにより被処理体の表面に結晶性珪素膜を堆積させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】少ない工数の追加でロジック回路とメタル容量素子とを混載し、かつ、ロジック動作特性の劣化を生じることがない半導体装置の製造方法を提供する。

【解決手段】基板11上に第1層間絶縁膜13を形成し、第1層間絶縁膜13に導電体柱14A、14Bを形成する。第1層間絶縁膜13の上面に溝配線部絶縁膜15を形成する。導電体柱14Bの上方において溝配線部絶縁膜15を除去して容量用開口部151を形成し、第1層間絶縁膜15の上面に容量素子用絶縁膜16を形成する。導電体柱14Aの上方において容量素子用絶縁膜16および第1層間絶縁膜15を除去して配線用溝152を形成する。容量用開口部151および配線用溝152に金属体17A、17Bを埋め込む。容量用開口部152の金属体17Aを容量素子の上部電極とし、配線溝152の金属体17Bをロジック配線とする。

(もっと読む)

昇圧回路および半導体メモリ

【課題】 高電圧の生成効率を向上し、消費電力を削減する。

【解決手段】 昇圧回路は、第1ノードおよび第2ノードの間に第3ノードを介して直列に接続された第1および第2キャパシタと、第4ノードおよび第5ノードの間に第6ノードを介して直列に接続された第3および第4キャパシタと、第4ノードが第1レベルに設定されているときに、第3ノードを電源線に接続する第1スイッチと、第1ノードが第1レベルに設定されているときに、第6ノードを電源線に接続する第2スイッチと、第6ノードの電荷を第2ノードに転送する第3スイッチと、第3ノードの電荷を第5ノードに転送する第4スイッチと、第2ノードを電圧線に接続する第5スイッチと、第5ノードを電圧線に接続する第6スイッチとを有する。

(もっと読む)

記憶装置、及び記憶装置の動作方法

【課題】書き替え動作を繰り返し行っても、高抵抗状態への書き込みレベルを所望の抵抗値に制御することが可能な記憶装置、及び記憶装置の動作方法を提供する。

【解決手段】電気抵抗の状態により情報を記憶・保持する遷移金属酸化物と前記遷移金属酸化物を挟む上下電極からなる抵抗変化型記憶素子からメモリセルが構成され、前記記憶素子の抵抗値が高い状態から抵抗値が低い状態へ変化させる動作及び変化後の状態を消去動作及び消去状態と定義し、前記記憶素子の抵抗値が低い状態から抵抗値が高い状態へ変化させる動作及び変化後の状態を書き込み動作及び書き込み状態と定義したとき、前記書き込み状態の伝導機構がトンネル伝導であり、トンネル抵抗を変化させることで2値以上の書き込み状態にすることが可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】HV系トランジスタでの閾値電圧の上昇を防止する半導体装置とその製造方法を提供する。

【解決手段】半導体基板10と、トランジスタ領域の半導体基板10を素子領域に分離する素子分離絶縁膜204と、トランジスタ領域に設けられた複数のトランジスタと、素子分離絶縁膜204の下に形成された反転防止拡散層209とを具備し、トランジスタは、素子領域上に形成されたゲート絶縁膜11と、ゲート絶縁膜11上に形成され素子分離絶縁膜204上に延びるゲート電極203と、ゲート電極203を挟むように半導体基板10表面に形成された拡散層18を有し、素子分離絶縁膜204は、素子領域に隣接する領域204−1と、領域204−1の底部より深い底部を有する領域204−2とを有し、反転防止拡散層209は、領域204−2の下に形成されている。

(もっと読む)

半導体記憶装置および半導体記憶装置の制御方法

【課題】複数のアンチヒューズ素子を同時にプログラムして処理速度を短縮する。

【解決手段】半導体記憶装置100は、それぞれトランジスタにより構成される第1のアンチヒューズ素子(A1)および第2のアンチヒューズ素子(A3)を含む。第1のアンチヒューズ素子および第2のアンチヒューズ素子は、同時にプログラム可能に構成され、第1のアンチヒューズ素子および第2のアンチヒューズ素子は、それぞれ、基板102上のPウェル130およびPウェル134に形成され、Pウェル130とPウェル134との間には、これらを分離する逆導電型のNウェル122やNウェル124が形成されている。

(もっと読む)

電子部品の製造方法

【課題】側壁転写プロセスにより複数層に形成された配線層を有する電子部品を簡便且つ安価な方法で得ること。

【解決手段】パターン27の側壁に沿った閉ループを有する側壁膜30を形成し、このパターン27を除去して前記側壁膜30を残存させた後この側壁膜30をマスクとして下地材料を選択的に除去する側壁転写プロセスを用いて下層配線層21を形成する第1の工程と、前記下層配線層21の上層に、前記側壁転写プロセスを用いて1層以上の上層配線層41,51を他の層22,23,24,42,43,44を介して形成する第2の工程と、前記下層配線層21および前記上層配線層41,51のそれぞれを切断するエッチングを一括で行うことにより、前記下層配線層21と前記上層配線層41,51に対して閉ループカットを施す第3の工程と、を含む。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

半導体記憶装置

【課題】信頼性が高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置1において、ワード線WLとビット線BLとの最近接点毎に、ピラー16a、16bを設ける。各ピラー16aにおいては、ダイオード22、バリアメタル23、陰極電極24、抵抗変化膜25及び陽極電極26をこの順に積層させる。そして、陰極電極24をP型シリコンにより形成する。

(もっと読む)

1,021 - 1,030 / 3,785

[ Back to top ]