国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,681 - 3,690 / 3,785

記憶素子及びその駆動方法

【課題】 記憶データの内容の判別が容易にできると共に、消費電力を低減することが可能な構成の記憶素子を提供する。

【解決手段】 一方の電極1と他方の電極2との間に異なる極性の電圧を印加することにより、抵抗状態が高抵抗状態と低抵抗状態との間を可逆的に変化する可変抵抗素子11,12を備え、2つの可変抵抗素子11,12において、一方の電極1を接続して共通端子Zとし、他方の電極2を独立させて端子X,Yを設けて、合計3端子X,Y,Zとしてメモリセルを形成した記憶素子10を構成する。

(もっと読む)

不揮発性メモリ

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリを提供する。

【解決手段】 本発明の不揮発性メモリは、クロスポイントメモリ構造または三次元構造を有する不揮発性メモリであって、対向する電極間に電気抵抗値が変化する金属酸化物を設け、前記対向する両電極のうち少なくとも一方の電極の金属酸化物と接触する面に電界集中部を設けたものである。

(もっと読む)

メモリ領域とロジック領域を混載する半導体装置の製造方法

【課題】 メモリ領域とロジック領域でのSTIの突き出し量のバラツキを低減するのと共に、ゲート写真製版のフォーカスマージンを向上し得る半導体装置の製造方法を得ることを目的とする。

【解決手段】 素子分離としてのSTI形成後の半導体基板において、メモリ領域のメモリセル部に対するチャネルドープ工程をゲート酸化前に行い、所定の不純物注入完了後にレジスト付きの状態にてフッ酸含有の溶液によりSTI段差を調整するためウエットエッチングを行い、メモリ領域とロジック領域のSTI突き出し量の差が同程度になるようにした。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】 本発明は、シャロートレンチアイソレーション(shallow trench isolation:STI)工程が適用されるフラッシュメモリ素子の信頼性を向上させ且つ縮小化を図ることが可能なフラッシュメモリ素子の製造方法を提供することを目的としている。

【解決手段】 半導体基板に突出構造の素子隔離膜を形成する段階と、傾斜イオン注入工程を行い、突出構造の素子隔離膜を含んだ全体構造上にイオン注入層を形成する段階と、前記イオン注入層を除去して前記突出構造の素子隔離膜をニップル構造の素子隔離膜に作る段階と、酸化工程でトンネル酸化膜を形成する段階と、前記ニップル構造の素子隔離膜の間に孤立形態のフローティングゲートを形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

不揮発性メモリとその製造方法

【課題】 対向する電極間に電気抵抗値が変化する金属酸化物を設け、低消費電力で駆動する低コスト、大記憶容量の低クロストークの特に携帯用機器のメモリとして最適な不揮発性メモリとその製造方法を提供する。

【解決手段】 本発明の不揮発性メモリの製造方法は、対向する電極間に未結晶状態又は不完全な結晶化状態の金属酸化物を設け、前記電極間に高電界エネルギーを印加することにより、発生するジュール熱のエネルギーによって結晶化した金属酸化物からなるメモリ・セル(メモリ領域)を形成する。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 冗長救済機能を備えた半導体記憶装置を有するロジック半導体装置において、半導体装置の高集積化に伴って生じる半導体装置の面積を増大させることなく、冗長救済を行なった後も、内部回路素子の金属配線における腐食の発生を防止する。

【解決手段】 半導体基板10上に形成された冗長救済されるべき回路素子を含む内部回路素子26と、半導体基板10上に内部回路素子26を覆うように形成された第1、第2及び第3の層間絶縁膜15、18及び21と、第3の層間絶縁膜21の上に形成された冗長救済されるべき回路素子26の冗長救済に用いられるヒューズ25とを備えている。第3の層間絶縁膜21とヒューズ25との間には、耐透水性を有する絶縁膜22が介在している。

(もっと読む)

自己スイッチングメモリデバイス

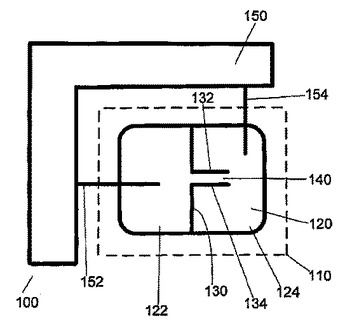

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

デュアルゲート誘電体構造を有する半導体素子の製造方法

【課題】ラジカル酸化(Radical Oxidation)によるデュアルゲート誘電体構造を有する半導体素子の製造方法を提供することを目的とする。

【解決方法】半導体基板上に絶縁膜を形成する工程と、該絶縁膜上に窒化膜を形成する工程と、所定領域の前記窒化膜を選択的にエッチングする工程と、前記エッチングされた窒化膜を含む全体構造上に酸化膜が形成されるようにラジカル酸化を実施する工程と、前記酸化膜上にゲート導電膜を形成する工程と、該ゲート導電膜と、前記酸化膜と、前記窒化膜、及び前記絶縁膜を選択的にエッチングする工程とを含み、前記所定領域に前記絶縁膜及び前記酸化膜が積層されて第1ゲート誘電体構造を形成し、前記所定領域以外の領域に前記絶縁膜、前記窒化膜、及び前記酸化膜が積層されて第2ゲート誘電体構造を形成する構成とした。

(もっと読む)

半導体装置の製造方法

【課題】EEPROMのメモリセルと容量素子とを同一半導体基板上に形成する際に、工程数の増加を防止して製造コストを低減する。また、容量素子の信頼性を改善し、メモリセルやMOSトランジスタ等の特性変動も防止する。

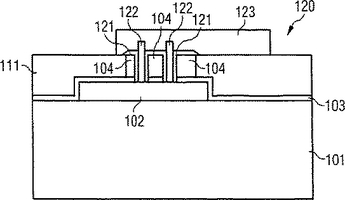

【解決手段】

P型シリコン基板1のメモリセル形成領域にはソース領域11に対して左右対称の一対メモリセルMC1,MC2が形成され、同じP型シリコン基板1の容量素子形成領域には、下部電極17と容量絶縁膜18と上部電極20から成る容量素子CAPが形成される。容量素子CAPの下部電極17は、一対メモリセルMC1,MC2のコントロールゲート22を形成するためのポリシリコン膜をパターニングすることで形成している。

(もっと読む)

3,681 - 3,690 / 3,785

[ Back to top ]