国際特許分類[H01L27/112]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | リードオンリーメモリ構造 (4,422)

国際特許分類[H01L27/112]の下位に属する分類

電気的にプログラム可能な読み出し専用メモリ (4,302)

国際特許分類[H01L27/112]に分類される特許

111 - 120 / 120

半導体記憶装置

【課題】 従来の半導体記憶装置においてダミービット線を複数用いて構成するレプリカ回路では、半導体製造技術の微細化によりトランジスタのオフリーク電流が増加したため、ダミービット線を充電する際にオフリーク電流により所望の電位に充電できなくなった。この結果、ダミービット線への充電時間あるいは放電時間も所望の時間とは異なるため、最適な動作タイミングの設定が出来ない。

【解決手段】 ダミーメモリセルアレイにおいて、第1のダミービット線25はドレイン領域21とダミービット線25とを接続するため、コンタクトおよびビアホール28〜30とメタル電極23,24を介して接続され、第2のダミービット線46はドレイン領域47とコンタクトしない構成とする。

(もっと読む)

フラッシュメモリをROMメモリへ変換する方法、およびその変換されたROMメモリを具えるデバイス

第1の半導体デバイス上のフラッシュメモリセルを、第2の半導体デバイス上のROMメモリセルに変換する方法であって、第1および第2の半導体デバイスのそれぞれは、半導体基板上に配置されて、同一のデバイス部、並びに、当該デバイス部をフラッシュメモリセルおよびROMメモリセルにそれぞれ配線するための、同一の書込みスキームをそれぞれ具え、フラッシュメモリセルは、少なくとも1つの不揮発性技術のマスクを用いて、不揮発性メモリ技術において製造され、さらに、アクセストランジスタ、並びに、浮遊ゲートおよび制御ゲートを含む浮遊トランジスタを具え、ROMメモリセルは、少なくとも1つのベースラインマスクを用いて、ベースライン技術において製造され、単一のゲートトランジスタを具え、少なくとも1つのベースラインマスクのレイアウトを操作するステップを含み、当該操作ステップは、フラッシュメモリセルのレイアウトを、少なくとも1つのベースラインマスクのレイアウトに組み込むステップと、少なくとも1つのベースラインマスクから、フラッシュメモリセルのレイアウトからの浮遊トランジスタのレイアウトを除去し、さらに、フラッシュメモリセルのアクセストランジスタのレイアウトを、ROMメモリセルのシングルゲートトランジスタのレイアウトとして設計することによって、少なくとも1つのベースラインマスクにおけるフラッシュメモリセルのレイアウトを、ROMメモリセルのレイアウトに変換するステップとを含む変換方法。  (もっと読む)

(もっと読む)

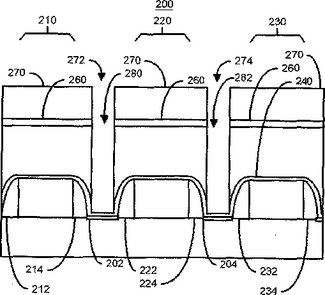

半導体セルの接触不良(contactdefect)を減らす方法とシステム

本発明は、半導体デバイス中に少なくとも1つのコンタクトを提供する方法およびシステムを提供する。半導体デバイスは、基板(201)、エッチング停止層(240)、このエッチング停止層(240)上にある層間絶縁膜(250)、層間絶縁膜(250)上にある反射防止(ARC)層(260)、およびエッチング停止層(240)より下にある少なくとも1つの構造を含んでいる。少なくとも1つのアパーチャを有しているとともに、このARC層(260)上にあるレジストマスクを提供する。このアパーチャは、ARC層(260)の露出した部分上方にある。この方法およびシステムは、エッチング停止層(240)を貫通してエッチングすることなく、露出したARC層(260)およびその下にある層間絶縁膜(250)をエッチングすることを含む。これにより、少なくとも1つのコンタクトホールの一部を提供する。この方法とシステムはまた、原位置でレジストマスクを除去し、少なくとも1つのコンタクトホールを原位置に提供すべく、コンタクトホールの一部において露出したエッチング停止層(240)の一部を除去し、コンタクトホールを導電材料で充てんすることを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】エンハンスメント型のMOS構造を有する半導体装置において、大きなリーク電流を発生させないようにする。

【解決手段】エンハンスメント型トランジスタにおいて、ゲート電極13下のチャネル領域に形成される高濃度P領域17を、ソース領域15bに接し、ドレイン領域15aに接しないようにする。このことによって、ドレイン領域15aと高濃度P領域17間のPN接合がなくなり、リーク電流を低減することができる。また、ドレイン領域15aと高濃度P領域17との距離は、ドレイン領域15aに動作電圧が印可されたときに拡がる空乏層が、高濃度P領域17の内部に拡がったとしても、空乏層内部の電界がアバランシェ降伏あるいはツェナー降伏を発生させる臨界電界に達しないような距離とする。これによりアバランシェ降伏あるいはツェナー降伏によるリーク電流の増大を抑制することができる。

(もっと読む)

MOS型電気ヒューズとそのプログラム方法、これを用いた半導体装置

【課題】MOS型電気ヒューズの電気的特性ばらつきを抑制する。

【解決手段】半導体ウェル中に形成されたMOSトランジスタ型電気ヒューズのプログラム方法において、ゲート電極に第1の電圧を印加し、ソース・ドレイン領域の一方に第1の電圧と異なる第2の電圧をかけ、ゲート電極とソース・ドレイン領域の一方との間のゲート絶縁膜のみを実質的に短絡させる。

(もっと読む)

集積メモリデバイスおよびその製造方法

【課題】容易に製造可能であり、セルのサイズの縮小を可能にするメモリデバイスを提供する。

【解決手段】 本発明の、トンネル電界効果トランジスタ(TFET)と埋込みビット線とを用いたメモリデバイスには、記憶セルの行および列を含む行列が含まれる。各記憶セルには、少なくとも1つのセルトランジスタ(T01〜Tmn)が含まれ、そのセルトランジスタは第1のドープされた領域と第2のドープされた領域とを含んでおり、一方がソース領域(98)であり、もう一方がドレイン領域(152)である。そのメモリデバイスにはワード線(T01〜Tmn)が含まれ、各ワード線は1つの行にあるメモリセルとビット線とに接続されており、各ビット線は1つの列における記憶セルに接続されている。第1のドープされた領域と第2のドープされた領域のドーピングタイプは異なる。

(もっと読む)

半導体集積回路装置

【課題】 リーク電流を低減させたROMを備えた半導体集積回路装置を提供する。

【解決手段】 ワード線とビット線の交点に設けられ、記憶情報に対応して上記ビット線に選択的にメモリ電流を流すようにされたMOSFETからなる複数のメモリセルと、アドレス信号に従って1つのワード線を選択するアドレス選択回路とを備えたROMにおいて、ゲート電圧制御回路又はアドレス選択回路とワード線との間にスイッチ素子を設け、スタンバイ状態のとき上記ゲート電圧制御回路により全ワード線を非選択レベルにし、又は上記スイッチ素子をオフ状態にして全ワード線をフローティング状態にする。

(もっと読む)

メモリ

【課題】メモリセルサイズを小さくすることが可能なメモリを提供する。

【解決手段】このメモリでは、選択トランジスタ11aと選択トランジスタ11bとは、ソース領域17を共有し、選択トランジスタ11aのゲート電極19aと選択トランジスタ11bのゲート電極19bとは、ワード線7と一体的に設けられ、かつ、平面的に見て、メモリセル9の形成領域におけるn型不純物領域14の延びる方向に対して斜め方向に延びるとともに、選択トランジスタ11aおよび11bの形成領域におけるn型不純物領域14と交差するように配置され、選択トランジスタ11aと選択トランジスタ11bとでn型不純物領域14を分割している。

(もっと読む)

半導体記憶装置

【課題】本発明は、データの読み出しを行うメモリセル周辺のセルデータやチップ上の位置によってセンスアンプの電圧マージンが低下することを防止することを特徴とする。

【解決手段】メモリ回路の1つのブロック内には複数の本体セルアレイ21、ダミーセルアレイ22、バイアス回路16、行デコーダ18、データ検出回路を構成するセンスアンプ23、基準電圧回路24が設けられる。上記本体セルアレイ21及びダミーセルアレイ22にはバイアス回路16で発生される直流バイアス電圧PRが供給される。データ検出回路を構成するセンスアンプ23は、データの読み出し時に本体セルアレイ21内の列線に対して所定のバイアス電圧SAINを供給してデータを検出する。基準電圧回路24は、ダミーセルアレイ22に所定のバイアス電圧REFINを供給することによって、上記センスアンプ23でデータを検出する際に使用される比較用基準電圧VREFを発生する。

(もっと読む)

半導体装置の製造方法

111 - 120 / 120

[ Back to top ]