国際特許分類[H01L27/112]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | リードオンリーメモリ構造 (4,422)

国際特許分類[H01L27/112]の下位に属する分類

電気的にプログラム可能な読み出し専用メモリ (4,302)

国際特許分類[H01L27/112]に分類される特許

31 - 40 / 120

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

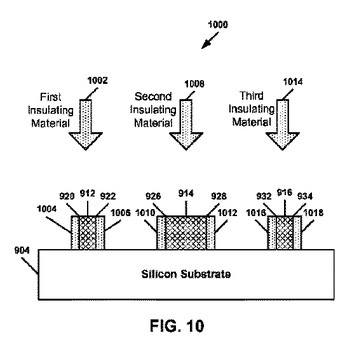

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】異なる構造の半導体メモリセルを備えた半導体メモリ領域を縮小化するための半導体装置を提供する。

【解決手段】半導体層に形成されるRAMの第1のトランジスタと、第1のトランジスタの第1のソース/ドレイン17に電気的に接続される第1電極を有するキャパシタQと、第1のトランジスタに隣接する領域の半導体層に形成されるROMの第2、第3のトランジスタと、第1のトランジスタの第2のソース/ドレイン16と第2のトランジスタの第1のソース/ドレイン20に電気的に接続されるビット線60とを有する。

(もっと読む)

超薄膜誘電体のブレークダウン現象を利用した半導体メモリセルセル及びメモリアレイ

【課題】 超薄膜誘電体のブレークダウン現象を利用した半導体メモリセルセル及びメモリアレイを提供する。

【解決手段】 超薄膜誘電体(312)の周りに構成されるデータ記憶素子(115)を有する半導体メモリセル(300)を使用し、超薄膜誘電体(312)にストレスを与えてブレークダウン(ソフトまたはハードブレークダウン)させてメモリセル(300)のリーク電流レベルを設定することにより情報を記憶する。セル(300)が引き込む電流を検知することによりメモリセル(300)からの読出しが行なわれる。適切と考えられる超薄膜誘電体(312)は約50オングストローム以下の厚さの高信頼度のゲート酸化膜である。

(もっと読む)

半導体装置

【課題】簡単な構成で多機能化を図った記憶回路を有する半導体装置を提供する。

【解決手段】複数のメモリセルのそれぞれは、第1と第2記憶ノードに交差接続された入力と出力がそれぞれ接続された第1と第2インバータ回路と、第1と第2記憶ノードと第1と第2入出力端子との間にそれぞれ設けられた第1、第2スイッチMOSFETと、第1記憶ノードと第3記憶ノードの間に設けられた第3スイッチMOSFETとを有する。第1と第2記憶ノードは、第1と第2入出力端子からの第1記憶情報が書き込み/読み出し可能にされる。第3記憶ノードは、第2記憶情報に対応して電源電圧又は接地電位が定常的に供給される。第3記憶ノードの記憶情報は、第3スイッチMOSFETをオン状態にして第1、第2記憶ノードに伝えられる。第1、第2スイッチMOSFETを介して第1と第2端子から読み出し可能にされる。

(もっと読む)

半導体素子の製造方法

【課題】半導体基板の損傷を最大限抑制して素子の漏洩電流発生が防止できる半導体素子の製造方法を提供する。

【解決手段】第1のコンタクトホールと、無結晶のポリシリコン膜及びPMD膜26を順次に形成してイオンを注入した後、金属配線を形成することによって、第1のコンタクトホールを用いてコーディングするので、その他のコーディング領域が別に必要でなくチップ面積を縮小することができ、PMDの蒸着前に第1のコンタクトホールを形成するので、半導体基板20の損傷を減らして漏洩電流が減少し、通常のROMコーディングとは反対にOFF特性で反対タイプのイオン注入によりON特性を有するようにし、金属配線の蒸着時に金属配線層の下部にポリシリコン膜が形成されて金属配線の断絶が最小化できる。

(もっと読む)

混載メモリ装置及び半導体装置

【課題】メモリセル領域の面積を削減できる混載メモリ装置を提供する。

【解決手段】本発明に係る混載メモリ装置は、SRAMと、ROMとを備える混載メモリ装置100であって、行列状に配置された複数の第1のメモリセル110及び複数の第2のメモリセル111とを備え、複数の第1のメモリセル110はそれぞれ、SRAMセル120とROMセル130とを含み、複数の第2のメモリセル111はそれぞれ、SRAMセル120を含み、かつROMセル130を含まず、複数の第1のメモリセル110はそれぞれ、少なくとも一つの第2のメモリセル111と隣接して配置される。

(もっと読む)

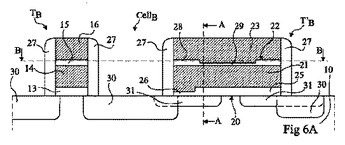

EEPROM構造を有する読出し専用メモリ

【解決手段】本発明は、少なくとも第1及び第2のメモリセル(CellB) を備えた不揮発性メモリ(M) に関しており、第1及び第2のメモリセルは、デュアルゲート(21,23) とデュアルゲート(21,23) 間に設けられた絶縁層(22)とを有する蓄積MOS トランジスタ(TB') を夫々備えている。第2のメモリセル(CellB) の蓄積トランジスタ(TB') の絶縁層(22)は、第1のメモリセルの蓄積トランジスタの絶縁層より絶縁性が低い少なくとも1つの部分(29)を有している。  (もっと読む)

(もっと読む)

マスクROMおよびマスクROMの製造方法

【課題】 プログラム層のレイヤを自在に変更でき、しかも、周辺回路のレイアウト設計等を変更する必要がなく、短期間で製品の納入が可能であり、かつ、歩留りが高いマスクROMを実現すること。

【解決手段】 メモリ部40において、ワード線ならびにビット線を多層配線で構成する。メモリ部40とロウブロック20との間に層変換部70aを設ける。メモリ部40とカラムブロック50との間に層変換部70bを設ける。層変換部70a,70bは、異なるレイヤの配線層間を電気的に接続するための多層配線構造体である。

(もっと読む)

新規ROMセルアレイ構造

【課題】メモリセルのセンスマージン低下を防止するメモリセルアレイ構造を提供する。

【解決手段】半導体メモリセルアレイは、長尺状に連続する活性領域220と、活性領域220に形成され、第1のメモリセル210[i]を構成する第1トランジスタと、活性領域220に形成され、第2のメモリセル210[i+1]を構成する第2トランジスタとを備える。第2のメモリセル210[i+1]は、活性領域220の長尺方向に沿って第1のメモリセル210[i]に最も近接する。半導体メモリセルアレイはさらに、第1及び第2トランジスタ間において活性領域220上に形成された分離ゲート235を備える。分離ゲート235は第1及び第2トランジスタのゲートとほぼ同じ構造を有し、所定電圧の供給を受けることにより、活性領域220において分離ゲート235の下方の部分を流れる活性電流を遮断する。

(もっと読む)

31 - 40 / 120

[ Back to top ]