国際特許分類[H03B5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396) | 増幅器の能動素子が半導体装置であるもの (289)

国際特許分類[H03B5/12]に分類される特許

41 - 50 / 289

プリントインダクタおよびその製造方法ならびに電圧制御発振器

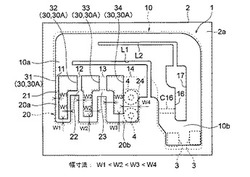

【課題】プリントインダクタのQ値を高く設定してもその形成面積を小さくすることができるなどの新規のプリントインダクタおよびその製造方法ならびに電圧制御発振器を提供する。

【解決手段】本実施形態のプリントインダクタ1は、第1のインダクタパターン10、第2のインダクタパターン20および接続部材30(例えば、第3のインダクタパターン30A)を備えている。第2のインダクタパターン20(または第1のインダクタパターン10)における遠方部分20a(または10a)の幅寸法は、その近接部分20b(または10b)の幅寸法よりも小さくなるように形成されている。

(もっと読む)

半導体集積回路

【課題】良好な高周波特性を維持しつつ、増幅器の使用周波数帯域切換えが可能な半導体集積回路を提供する。

【解決手段】結合係数k1を有し、互いに並列に接続されるコイルL11及びコイルL12と、コイルL11及びコイルL12に直列に接続されるコイルL13と、コイルL11に並列に接続されるコンデンサC11と、コイルL12に並列に接続されるコンデンサC12と、コイルL11の一端と、コンデンサC11の一端とに接続される入力端子p1と、コイルL12の一端と、コンデンサC12の一端とに接続される入力端子n1と、入力端子p1と、入力端子n1とにそれぞれ逆位相の入力信号を供給する入力信号供給部200とから構成されることを特徴とする半導体集積回路。

(もっと読む)

半導体チップ、筺体内信号伝送方法及び筺体内信号伝送システム

【課題】同一の筺体内に配置された半導体チップ間でミリ波の信号伝送媒体を介したミリ波帯域の信号を伝送できるようにすると共に、当該半導体チップ間でより簡易に高速伝送システムを実現できるようにする。

【解決手段】入力信号SINが基準搬送信号Sfに基づいてミリ波の送信信号Soutに変換され、変換後の送信信号Soutが、筺体1内に配置されたCMOSチップ101の送信部から当該筺体1内のミリ波の信号伝送媒体51へ伝送される場合であって、局部発振信号Sf’を発振する発振回路を有して筺体1内に配置され、信号伝送媒体51から受信したミリ波の受信信号Sinを発振回路に注入して当該局部発振信号Sf’を基準搬送信号Sfに同期させ、同期後の局部発振信号Sf’に基づいてミリ波の復調信号SOUTを復元するものである。

(もっと読む)

低位相ノイズ電圧制御発振器

本発明の形態は、消費電力を低減し位相ノイズ性能を向上させるために、電流再使用技術を用いた低位相ノイズ発振器回路を含み、発振器回路は、第2のVCOに結合されている第1のVCOを備え、第1及び第2のVCOの出力は、コンデンサ等の受動素子に結合されている。第1及び第2のVCO両方の全体の消費電力は、単一のVCOの消費電力と略同じである。また、位相ノイズは、約3dBほど低減される。このため、発振器回路の消費電力を増加させることなしに、位相ノイズ性能が向上される。 (もっと読む)

電圧制御発振器

【課題】電界効果トランジスタのドレイン−ソース間容量のばらつきによる位相誤差を低減しつつ、位相が互いに90°ずつ異なる発振信号を生成する。

【解決手段】電界効果トランジスタM1のドレインと電界効果トランジスタM2のドレインとの間にインダクタL1を接続し、電界効果トランジスタM3のドレインと電界効果トランジスタM4のドレインとの間にインダクタL2を接続し、インダクタL1にインダクタL3を磁気的に結合し、インダクタL2にインダクタL4を磁気的に結合し、インダクタL3の一端とインダクタL4の一端とをコンデンサC1を介して容量結合し、インダクタL3の他端とインダクタL4の他端とをコンデンサC2を介して容量結合する。

(もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

電圧制御発振器

【課題】マイクロストリップラインのトリミングによってQ値の劣化を招くことなく、各種の周波数帯への調整を可能とする。

【解決手段】電圧制御発振器は、発振用トランジスタのベースに接続された共振回路を有しており、この共振回路には、バラクタダイオードとともにマイクロストリップライン10が設けられている。マイクロストリップライン10は、その一端が制御端子に接続されており、他端がビア7を介してグランド電極に接続されている。またマイクロストリップライン10は、その一端に位置する入力導体部10bから他端に位置する接地導体部10eに至る導電路がスパイラル形状をなしており、導電路の途中が粗調用導電体10aを介してグランドに接続されている。

(もっと読む)

高周波発振器

【課題】位相雑音特性を劣化させることなく出力電力を増大可能な高周波発振器を得る。

【解決手段】発振用の能動素子として用いられるバイポーラトランジスタ1と、バイポーラトランジスタ1のベース端子またはゲート端子に一端が接続されるとともに、他端が接地され、所定の発振周波数において誘導性を有するインダクタ2と、バイポーラトランジスタ1のコレクタ端子またはドレイン端子に一端が接続されるとともに、他端が接地され、発振周波数において誘導性を有するインダクタ3と、バイポーラトランジスタ1のエミッタ端子またはソース端子に一端が接続されるとともに、他端が接地され、発振周波数において容量性を有するキャパシタ4と、を備えた直列帰還型の高周波発振器であって、ベース端子またはゲート端子と、コレクタ端子またはドレイン端子との間に直列接続され、入力された信号の位相を変化させる移相回路5をさらに備えたものである。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

高周波発振回路

【課題】発振回路の発振周波数を広帯域に制御可能でIC化に適した比較的小規模な発振回路を提供する。

【解決手段】一方の電源に接続される電流源と、他方の電源に接続されて誘導起電力によって電流を変動させる1組の負荷インダクタと、前記電流源と前記負荷インダクタとそれぞれに結合する1組の差動回路と、前記一方の差動回路の入力と前記他方の差動回路の出力との間に抵抗値を制御可能な可変抵抗を備えて正帰還が掛るように構成されて、前記可変抵抗の抵抗値に対応して発振周波数が定まる高周波発振回路である。

(もっと読む)

41 - 50 / 289

[ Back to top ]