国際特許分類[H03B5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396) | 増幅器の能動素子が半導体装置であるもの (289)

国際特許分類[H03B5/12]に分類される特許

51 - 60 / 289

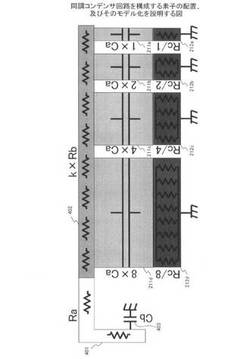

共振器型発振器、及び同調コンデンサ回路

【課題】共振器型発振器のQ値などの特性を高く維持させた設計をより容易に行えるようにする技術を提供する。

【解決手段】静電容量Caの2n倍(nは0〜5までの整数)となっている計6個)のコンデンサ211a〜fが並列に接続され、それらコンデンサ211a〜fにはスイッチ212a〜fがそれぞれ直列に接続されている。コンデンサ211a〜fは、静電容量が大きいものほど、インダクタと接続させる配線402の長さが短い位置に配置されている。それにより、出力する信号の周波数が低くなるほど、配線402の抵抗がQ値に及ぼす影響を低減させる。

(もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

電圧制御発振器

【課題】残留位相雑音特性を劣化させずに発振周波数の広帯域化を実現する電圧制御発振器を提供することを目的とする。

【解決手段】制御電圧印加端子Vc1からの制御電圧に応じて所望の周波数で発振する能動回路を備えた電圧制御発振器であって、前記能動回路は、トランスTSの一次側コイルL5に印加される前記制御電圧によってインダクタンス値が変化する二次側コイルL3を発振維持用のチョークコイルとして用いる。コイルL3のインダクタンス値が変化することで、コイルL3とコンデンサC5との共振周波数を変化させられる。その結果、制御電圧により、共振回路のバリキャップダイオードD1によるリアクタンス特性の変化だけでなく、能動回路のリアクタンス特性を変化させられる。

(もっと読む)

インダクタを備えた半導体集積回路

【課題】半導体集積回路をパッケージに実装した後に、インダクタンスを増加および減少させる調整が可能な半導体集積回路を提供する。

【解決手段】LSIの内部回路106が形成された同一の半導体基板に磁気検出素子100が形成されており、ボンディングパッド114とLSIの内部回路106の間に接続された第1インダクタ101のインダクタンスを磁気検出素子100と磁気検出回路105の出力電圧でモニタし、第1インダクタ101の片方の端子と第2インダクタ102の一端と第3インダクタ103の一端が第1接続部107を介して接続される第1スイッチ108、第2インダクタ102の片方の端子が第2接続部109を介して接続される第2スイッチ110、および、第3インダクタ103の片方の端子が第3接続部111を介して接続される第3スイッチ112を接続または切断状態に切り替えることにより、第一のインダクタ101をトリミングする。

(もっと読む)

増幅器および発振器

【課題】MOSトランジスタの高周波領域におけるトランスコンダクタンスの劣化を招くことなく、低消費電力化を図ることが可能な増幅器などの提供。

【解決手段】この発明は、MOSトランジスタQ1などを含む増幅器である。MOSトランジスタQ1のゲートには第1の入力信号が入力され、MOSトランジスタQ1のバルクには第2の入力信号が入力され、MOSトランジスタQ1のソースから出力信号が出力される。そして、第1の入力信号と第2の入力信号とは同相の信号である。

(もっと読む)

設定可能ワイドチューニングレンジ発振器コア

発振器は、共振器と、第1および第2のp型トランジスタと、第1および第2のn型トランジスタとを含む。共振器は、第1の端子と第2の端子とを持つ。第1のp型トランジスタは、第1の端子にスイッチ可能に接続されており、第2のp型トランジスタは、第2の端子にスイッチ可能に接続されている。第1のn型トランジスタの第1のドレインと第2のn型トランジスタの第2のドレインとは、それぞれ、第1の端子および第2の端子に電気的に接続される。発振器はNMOSのみモードおよびCMOSモードで作動可能である。 (もっと読む)

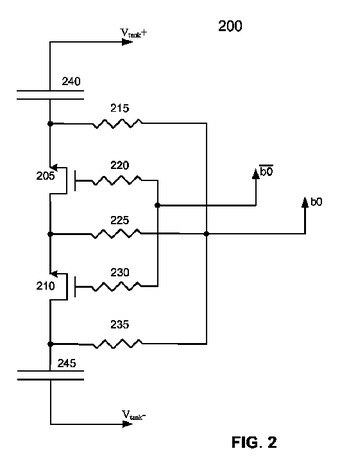

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

半導体回路

【課題】安定した動作を行うことができる半導体回路を提供することを課題とする。

【解決手段】ソースが第1の電位ノードに接続される第1のpチャネルトランジスタ(201)と、ソースが第2の電位ノードに接続される第1のnチャネルトランジスタ(202)と、ゲートが第1のnチャネルトランジスタのドレインに接続され、ドレインが第1のnチャネルトランジスタのゲートに接続される第2のpチャネルトランジスタ(203)と、ゲートが第1のpチャネルトランジスタのドレインに接続され、ドレインが第1のpチャネルトランジスタのゲートに接続される第2のnチャネルトランジスタ(204)と、第1のpチャネルトランジスタ及び第1のnチャネルトランジスタのドレイン間に接続される第1の抵抗(301,302)と、第2のpチャネルトランジスタ及び第2のnチャネルトランジスタのドレイン間に接続される第2の抵抗(303,304)とを有する。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

51 - 60 / 289

[ Back to top ]