国際特許分類[H03B5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396) | 増幅器の能動素子が半導体装置であるもの (289)

国際特許分類[H03B5/12]に分類される特許

31 - 40 / 289

広帯域発振回路

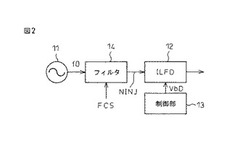

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

半導体集積回路装置および発振周波数較正方法

【課題】発振器の発振周波数の較正作業を短縮することができる半導体集積回路装置および発振周波数較正方法を提供する。

【解決手段】DCO50と、温度に対して単調な特性を持って変化する電圧源20から得られる電位に応じたDCO50に設定すべき発振周波数の温度係数および発振周波数の絶対値を記憶する記憶部42と、を備えたことを特徴とする半導体集積回路装置。

(もっと読む)

半導体装置

【課題】同相信号除去比を高めた発振信号を得ることができる半導体装置を提供する。

【解決手段】半導体基板と、前記半導体基板上に第1の絶縁膜を介して設けられた第1の電極4と、前記第1の電極上に第2の絶縁膜を介して設けられ前記第1の電極との間に第1のキャパシタを形成する第2の電極6と、前記第1の電極上に前記第2の絶縁膜を介して設けられ前記第1の電極との間に第2のキャパシタを形成する第3の電極7と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続されたインダクタ19と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続された増幅回路20と、を備えたことを特徴とする半導体装置。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

電圧制御発振回路

【課題】簡単な回路構成で応答性をよくし、切り替えられる発振信号の各周波数で同一電圧振幅を得られる電圧制御発振回路を提供する。

【解決手段】LCタンク回路1に第1及び第2のキャパシタ群11,12を備える、第1及び第2のキャパシタ群11,12はそれぞれ2つのキャパシタC1,C2を備える。負性コンダクタンス部2により、LCタンク回路1の共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成し、2つの出力端out1,out2から出力する。電流源31,32からなる電流源3から負性コンダクタンス部2を介してLCタンク回路1に電流を供給する。制御信号を、CMOSスイッチからなる電流源スイッチ4,第1キャパシタスイッチ5及び第2キャパシタスイッチ6に与え、電流源群3から供給する電流とLCタンク回路1のキャパシタンスを切り替える。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

電圧制御発振器

【課題】コルピッツ回路を用いた電圧制御発振器において、帰還部の2つのコンデンサ間とトランジスタのエミッタとを接続する導電線路におけるインダクタンス成分の影響による出力周波数の可変幅(調整幅)の劣化(低下)を抑えることのできる電圧制御発振器を提供すること。

【解決手段】コルピッツ回路を用いたVCOにおいて、帰還部2のコンデンサ22、23について、トランジスタ21のベースから伸びる端子部8(T1)及び前記トランジスタ21のエミッタから伸びる端子部8(T2)が夫々装着されるベース基板5上のベース用端子(接続部7)とエミッタ用端子とを直結するように第1の帰還容量素子(コンデンサ)22を配置すると共に、上記エミッタ用端子とアース用端子(接地電極51)とを直結するように第2の帰還容量素子(コンデンサ)23を配置する。

(もっと読む)

発振回路及び半導体装置

【課題】周波数可変範囲の広い発振回路及び発振回路を備えた半導体装置を提供する。

【解決手段】第1の端子と第2の端子との間に接続されたインダクタンス素子と、インダクタンス素子と並列に第1の端子と第2の端子との間に接続された増幅回路と、第1の端子及び第2の端子に接続された第1の容量素子と、を備えた共振型発振回路であって、インダクタンス素子の配線の途中に2箇所以上の引き出し部を設け、2箇所以上設けた引き出し部の間にオンしたときに当該引き出し部間を短絡するスイッチ素子と第2の容量素子とが並列に接続されている。

(もっと読む)

31 - 40 / 289

[ Back to top ]