国際特許分類[H03B5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396) | 増幅器の能動素子が半導体装置であるもの (289)

国際特許分類[H03B5/12]に分類される特許

61 - 70 / 289

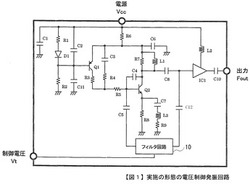

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

電圧制御発振器

【課題】変調感度が高すぎず、かつ、制御周波数範囲の広い電圧制御発振器を提供する。

【解決手段】構造、容量変化特性が異なる複数種類の可変容量素子が並列に接続され、制御電圧により、複数種類の可変容量素子の容量値を同時に制御するようにした共振部と、共振部による発振を維持するための増幅部とを備える。可変容量素子として、バラクタダイオードとMOSバラクタを用いることができる。

(もっと読む)

電圧制御発振器

【課題】電源ラインなどから入力する外来ノイズの影響を低減できる電圧制御発振器を提供すること。

【解決手段】

発振トランジスタ11のベース・エミッタ間に第1の帰還コンデンサ12を接続し、発振トランジスタ11のエミッタ・コレクタ間に第2の帰還コンデンサ13を接続し、発振トランジスタ11のベース・コレクタ間にインダクタ14を接続してコルピッツ発振回路を構成する。発振トランジスタ11のコレクタと直流電源端子18との間にコレクタバイアス抵抗30を接続し、コンデンサ19を介してコレクタバイアス抵抗30の一端を接地する。発振トランジス11のコレクタとベースとの間にチョークインダクタ31とコンデンサ32とが直列に接続されたフィルタ回路を接続する。

(もっと読む)

電圧制御発振器

【課題】低電源電圧の条件下にあっても、安定した発振の起動及び持続を保証しつつ低位相雑音化を達成することができる電圧制御発振器を提供する。

【解決手段】制御入力電圧に応じてインピーダンスが変化するLC並列共振回路と、該LC並列共振回路に負性抵抗を導入する負性抵抗回路と、を含む電圧制御発振器において、該負性抵抗回路が、該LC並列共振回路に並列に設けられ、キャパシタを介してクロスカップリングされた第一のトランジスタ対を有し、該第一のトランジスタ対の各トランジスタのゲートが第一のバイアス電圧にバイアスされて、C級増幅動作をする第一の増幅回路と、同様の回路構成を有し、各トランジスタのゲートが該第一のバイアス電圧と異なる第二のバイアス電圧にバイアスされて、C級増幅動作をする第二の増幅回路と、を少なくとも含む。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

61 - 70 / 289

[ Back to top ]