国際特許分類[H03B5/36]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が電気機械的振動子であるもの (2,343) | 圧電気振動子であるもの (2,069) | 増幅器の能動素子が半導体装置であるもの (86)

国際特許分類[H03B5/36]に分類される特許

31 - 40 / 86

電子デバイス

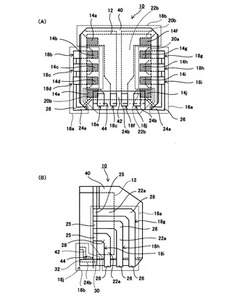

【課題】検査・書込み用端子と実装用端子との間のショートを抑制することのできる構造の電子デバイスを提供する。

【解決手段】端子形成面に複数の接続端子14a〜14jが形成されているパッケージ部品12と、樹脂部40と、複数のリード18a〜18jとを備え、接続端子14a〜14jは、端子形成面の外形において対向する一対の辺に沿って形成され、複数のリード18a〜18jは、第1リード群16aと第2リード群16bを有し、第1リード群16aは、端子形成面上において前記一対の辺から外側に向かって延設され、第2リード群16bは、端子形成面上において2列に形成された接続端子14a〜14j間を通して前記一対の辺に交差する他の辺から端子形成面の外側へ延設されることを特徴とする。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

発振確認検査方法

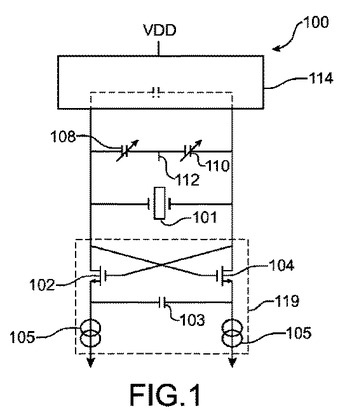

【課題】検査に要する時間を短縮するとともに、水晶発振回路単独の特性を検査すること。

【解決手段】CMOSインバータ112を含む発振増幅回路104を備えていて、CMOSインバータに並列に水晶振動子が接続されることにより発振する水晶発振回路100の発振確認検査をするに当たり、発振増幅回路の出力端子XTを接地し、及び、発振増幅回路104の入力端子XTBを電気的に浮遊させ、出力端子を流れる電流量を測定する。

(もっと読む)

広い周波数変化範囲を有する電気共振器デバイス

可変周波数ωで動作できる電気共振器デバイスであって、少なくとも、音響共振器と、共振器に並列に結合され、虚数部が

ただしC1≧0、に等しい調整可能な複素インピーダンスを有する第1の電気回路と、前記共振器および前記第1の電気回路に並列に結合され、虚数部が

ただしC2<0、に等しい複素インピーダンスを有する第2の電気回路とを含み、ωが前記デバイスの動作周波数であることを特徴とする。  (もっと読む)

(もっと読む)

発振回路

【課題】不要な周波数での発振を防ぐと共に、期待周波数での安定した発振を実現する。

【解決手段】発振回路100は、発振素子110と、反転増幅器120と、状態保持回路130を備える。発振素子110と反転増幅器120の入出力が互いに接続されて発振ループを構成する。状態保持回路130は、反転増幅器120の出力に同期して、反転増幅器120の出力論理を所定期間固定し、この期間内に反転増幅器120の出力状態を保持する。この所定期間は、期待発振周波数に対応する周期の半分より短く設定されている。

(もっと読む)

能動的バイアスを用いた低電力消費クォーツ発振器

クォーツ発振器回路は、能動的分岐を形成するように供給電圧源の2つの端子の間で電流源(4)と直列に実装された2つの相補するPMOS及びNMOSトランジスタ(P1、N1)を備えるインバータを含む。PMOSトランジスタ(P1)のソース端子は電流源に接続され、もう一方のNMOSトランジスタ(N1)のソース端子は接地端子に接続される。これらのトランジスタのドレイン端子は、出力においてクォーツ(3)の第1の電極(XOUT)に接続され、これらのトランジスタのゲート端子は、入力においてクォーツの第2の電極(XIN)に接続される。第1の位相シフト・コンデンサ(C1)は、クォーツの第1の電極に接続され、第2のコンデンサ(C2)は、クォーツの第2の電極に接続される。発振器回路は、インバータ・トランジスタのドレイン端子とゲート端子との間に配列された能動的バイアス手段(2)を含む。これらのバイアス手段は、クォーツ内で振動を発生させるための能動的分岐の相互コンダクタンスを損なわないように十分に高いインピーダンス値を有するフォロワ実装演算相互コンダクタンス増幅器とすることができる。  (もっと読む)

(もっと読む)

高周波発振回路

【課題】高価なFETを用いることなく、例えば10GHz以上の高周波数波帯で用いる場合にも使用可能で、広帯域化を図った高周波発振回路を構成する。

【解決手段】デプレッション型のNチャネルFETからなる発振回路用FET Q1のゲートを直列帰還素子である線路SL1を介して接地し、デプレッション型のNチャネルFETからなるバッファアンプ用FET Q2のソースをキャパシタC2を介して高周波的に接地し、バッファアンプ用FET Q2のゲートと発振回路用FET Q1のドレインとを直流的に導通する第1のインピーダンス回路Z1を介して接続し、バッファアンプ用FET Q2のソースと発振回路用FET Q1のドレインとの間に直流的に導通する直流抵抗成分を含む第2のインピーダンス回路Z2を接続し、発振回路用FET Q1のソースと接地との間に直流的に導通する直流抵抗成分を含む第3のインピーダンス回路Z3を設ける。

(もっと読む)

発振制御装置及び発振器

【課題】出力信号に含まれる高調波成分が少なく、低電圧で動作可能な発振制御装置を提供すること。

【解決手段】発振制御装置は、振動子を発振させる発振部と、直列接続された2つの同じ型のトランジスタを有し、発振部から出力された発振信号に応じた信号を2つのトランジスタの接続点から出力する出力増幅回路と、2つのトランジスタの各ゲートに印加する、直流の2つの異なるレベルのバイアス電圧を発生するバイアス部と、発振部に定電圧を印加する定電圧電源部と、発振部から2つのトランジスタのゲートのいずれか一方の間に設けられ、発振部から出力された発振信号の位相を反転させるインバータ部とを備える。2つのトランジスタの一方のゲートには、発振部から出力された発振信号及び2つのバイアス電圧の一方が印加され、2つのトランジスタの他方のゲートには、発振部から出力されインバータ部によって位相が反転された発振信号及び2つのバイアス電圧の他方が印加される。

(もっと読む)

高周波発振回路

【課題】高価なFETを用いることなく、例えば10GHz以上の高周波数波帯で用いる場合にも使用可能で、広帯域化を図った高周波発振回路を構成する。

【解決手段】発振回路用FET Q1のゲートを直列帰還素子である線路SL1を介して接地し、発振回路用FET Q1のソースをインダクタL3を介して直流的に接地し、バッファアンプ用FET Q2のドレインをインダクタL1を介して電源端子Vdに接続し、バッファアンプ用FET Q2のソースをキャパシタC2を介して高周波的に接地し、且つバッファアンプ用FET Q2のソースを直流電流経路用インダクタL2を介して発振回路用FET Q1のドレインに接続する。また、バッファアンプ用FET Q2のゲートと発振回路用FET Q1のドレインとの間を直流カットキャパシタC1および線路SL2を介して接続し、この電気長を発振周波数の1/2波長未満とする。

(もっと読む)

発振器及び発振器を備えた電子機器

【課題】負性抵抗の減少を防止し、低消費電力化。

【解決手段】第1の端子Aと、第2の端子Bと、第1の端子Aと第2の端子Bとの間に接

続された振動子OSCと、第1の端子Aと接地電位を供給する接地線GNDとの間に接続

された第1のコンデンサCgと、第2の端子Bと接地線GNDとの間に接続された第2の

コンデンサCdと、第1の端子Aと第2の端子Bとの間にm個(mは3以上の奇数)のイ

ンバータIN1〜IN3が直列に接続されたインバータ列と、インバータ列の入力側から

数えてn番目(nは1≦n<mの整数)のインバータの入力端子とn+1番目のインバー

タの出力端子との間に接続された第3のコンデンサCfと、を含む、ことを特徴とする発

振器100。

(もっと読む)

31 - 40 / 86

[ Back to top ]