国際特許分類[H03K17/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698)

国際特許分類[H03K17/00]の下位に属する分類

スイッチ動作の高速化のための変形 (141)

完全導通状態を確保するための変形 (176)

過電流または過電圧に対するスイッチ回路の保護のための変形 (526)

最大許容被開閉電圧を増大させるための変形 (45)

最大許容被開閉電流を増大させるための変形 (21)

零交叉でスイッチ動作するための変形 (11)

物理量,例.温度,の変化を補償するための変形 (96)

混信電圧または混信電流を消去するための変形 (505)

スイッチの状態を表示するための変形 (2)

磁心スイッチ素子を所定の状態にリセットするための変形

供給電圧の投入時に所定の初期状態を確保するための変形 (300)

制御パルス受信後に一時的な阻止動作を行わせるための変形 (1)

スイッチ動作の前に時間遅延を導入するための変形 (58)

2以上のスイッチング動作を実行するために時間間隔の選択ができ,かつ,プログラムが完了された後,自動的に動作を終わらせるための変形 (24)

スイッチ動作の前に所定のしきい値を設けるための変形 (99)

特定の構成要素の使用によって特徴づけられたもの (2,578)

制御信号が発生される方法により特徴づけられるもの (510)

国際特許分類[H03K17/00]に分類される特許

101 - 110 / 605

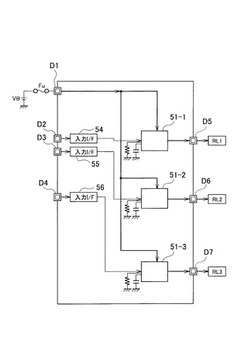

過電流保護装置及び過電流保護システム

【課題】同一の電源に接続された複数の過電流保護装置どうしで、リトライ動作を実行するタイミングに時間差を持たせることが可能な過電流保護装置、及び過電流保護システムを提供する。

【解決手段】IC回路51-1のFET(Q1)をオンとした際に、バッテリ電圧VBAが閾値電圧以下となった場合には、各IC回路のFET(Q1)を全てオフとし、更に、FET(Q1)のオンからバッテリ電圧VBAが閾値電圧以下となるまでの時間を計時する。この時間が400μsec未満であれば、カウント値Nをインクリメントする。その後、ランダムに設定された待機時間Tpが経過した後、再度FET(Q1)をオンとする動作を繰り返し、カウント値Nが7に達した時点で、IC回路51-1のFET(Q1)をオフ状態に保持する。従って、デッドショートの発生している負荷駆動用の回路のみを確実に停止させ、それ以外の負荷駆動用の回路の駆動を継続させることができる。

(もっと読む)

検出回路とそれを用いた半導体装置

【課題】本発明は、安価かつ容易に歪特性の劣化を抑制できる検出回路とそれを用いた半導体装置を提供することを目的とする。

【解決手段】電力増幅器とアンテナの間に配置された方向性結合器の結合線路両端の信号を用いて、該電力増幅器の歪特性劣化を検出する回路であって、該結合線路の結合端子の電力を移相および減衰する移相・減衰器と、該移相・減衰器からの出力電力と、該結合線路のアイソレーション端子の電力の差分を出力する手段と、該差分をDC信号に変換する検波回路と、該DC信号の電圧レベルが所定値よりも高いかを判定する比較回路とを備える。そして、該移相・減衰器は、該電力増幅器の歪特性が劣化する該アンテナ端の負荷状態において、該移相・減衰器が出力する信号の位相が該アイソレーション端子の信号の位相と180°の位相差になるように該結合端子の電力を移相することを特徴とする。

(もっと読む)

適応標本化装置および適応標本化プログラム

【課題】入力信号のフレームを標本化する場合に、入力信号の性質に応じた不等間隔で標本化を行う技術を提供する。

【解決手段】適応標本化装置1Aは、フレーム記憶手段10と、フレームに対して、標本点数を減らした複数の異なる標本化間隔で標本化して縮小信号とし、この縮小信号群を出力する階層化信号縮小手段20と、この各縮小信号を入力信号と同じ標本化間隔に戻して、フレームとの誤差をブロックごとに定量化し誤差信号として出力する階層化誤差演算手段30と、フレームの各ブロックに対して適用する標本化間隔の割り当て方である標本化パターンを複数記憶する標本化パターンデータベース50と、各誤差信号と、標本化パターンとに基づき、誤差を最適化する標本化パターンを探索する最適化手段70と、この最適化手段が求めた標本化パターンに基づき、入力信号のフレームを標本化し、出力信号として出力する標本選択配置手段80と、を備える。

(もっと読む)

電子回路

【課題】増幅回路の雑音指数の劣化を抑制すること。

【解決手段】送信端子Txから入力された送信信号を前記共通端子ANTに接続する送信スイッチSW1と、前記共通端子から入力された受信信号を増幅し、受信端子Rxに出力する増幅回路90と、前記共通端子から他のスイッチを介さず入力された前記受信信号を前記増幅回路に接続する第1受信スイッチSW2と、前記共通端子と前記受信端子との間で前記第1受信スイッチとは並列に接続され、前記共通端子から入力された前記受信信号を前記増幅回路とは別の経路で前記受信端子に接続する第2受信スイッチSW3と、を具備する電子回路。

(もっと読む)

負荷駆動制御装置

【課題】消費電力を抑えつつ、高輝度で安定した駆動を得るとともに駆動制御回路全体の寿命を向上させる。

【解決手段】負荷20に接続される駆動制御部10を備え、駆動制御部10は、負荷20の定格電流値IFと、パルス駆動したときの絶対最大定格電流値Imaxから予め設定されたピーク電流値Ipに基づいてパルス幅変調することで、負荷20のオン期間を規定した第1のオン/オフ周期による第1駆動パルスP1を生成し、第1のオン/オフ周期のオン期間の中でさらにスイッチングさせることで、パルスの最大振幅がIpとなるように、第2のオン/オフ周期による第2駆動パルスP2を生成する定電流パルス駆動部14とを備え、第2駆動パルスP2によって駆動された電流を前記負荷20に印加することによって、負荷20を連続的に駆動させるとともに、充放電制御部15のキャパシタンスC1を信頼性寿命の高いセラミックコンデンサーを使用した。

(もっと読む)

多数の容量性センサ素子の静電容量を決定するための回路装置

【課題】 n個の容量性センサ素子(SE1〜SEn)の静電容量を決定するための回路装置であって、それらのそれぞれの静電容量が作動に基づいて変化するものを提供する。

【解決手段】 この回路装置は、少なくとも一つの集電コンデンサー(CS1〜CSm)、参照電圧源(RQ)、少なくとも一つの集電コンデンサーに電気的に連結され、かつそれぞれのセンサ素子の静電容量を決定するために少なくとも一つの集電コンデンサーに存在する電圧を評価する評価装置(AE)、少なくとも一つの制御信号(SS1〜SSk)を発生するための制御装置(MC)、及び参照電圧源に及び少なくとも一つの集電コンデンサーに電気的に連結され、かつ少なくとも一つの制御信号が付与される少なくとも一つの集積回路(IC1〜ICm)を含む。この少なくとも一つの集積回路は、k個の切換スイッチ(WS1〜WSk)を含み、それぞれの切換スイッチがn個のセンサ素子の一つとそれぞれ組み合わされており、それぞれの切換スイッチの切換位置が少なくとも一つの制御信号に依存しており、それぞれの切換スイッチが、それぞれ組み合わされたセンサ素子を第一切換位置で参照電圧源に連結し、かつそれぞれの切換スイッチが電荷移動の目的のためにそれぞれ組み合わされたセンサ素子を第二切換位置で少なくとも一つの集電コンデンサーに連結する。

(もっと読む)

断線検出回路

【課題】ノイズなどの不要成分の影響を極力抑制して信頼性良く断線検出できるようにする。

【解決手段】電源Vc−グランド間には、負荷M、MOSトランジスタM1、抵抗R1が直列接続されている。第1電圧検出回路3は抵抗R1の端子電圧を検出する。制御回路2は、第1電圧検出回路3により検出された抵抗R1の検出電圧について閾値電圧ref1と比較した検出結果に基づいて断線を検出する。

(もっと読む)

デジタル信号出力回路

【課題】スイッチ素子を用いて電源を負荷に接続また切り離し、出力端子の電圧を測定して故障を判定する構成のデジタル信号出力回路を2台並列接続して2重化する構成では、待機側デジタル信号出力部のスイッチ素子が故障すると制御側が故障であると誤検出する。この発明では、このような故障を防止することを目的にする。

【解決手段】スイッチ素子51a(51b)に直列にスイッチ素子52a(52b)を接続し、これらのスイッチ素子の接続点の電圧を電圧リードバック部54a(54b)で測定してスイッチ素子の故障を判定するようにした。待機側デジタル信号出力部50bの状態に影響されずスイッチ素子51aの故障を判定でき、かつスイッチ素子51bのオン故障を判定できる。このため、誤検出が発生することがなく、かつ切り換える前に待機側デジタル信号出力部50bの故障を判定できる。

(もっと読む)

ポジションスイッチの出力判定装置

【課題】長期間使用した場合でも、常に適正なスイッチ位置の判定を行うことができるポジションスイッチの出力判定装置を提供する。

【解決手段】本発明に係わるポジションスイッチの出力判定装置(20)は、少なくとも2つの位置間の変位により、第1電圧レベルまたは当該第1電圧レベルと異なる第2電圧レベルとを出力するポジションスイッチ(10)の出力判定装置であって、前記第1電圧レベルと前記第2電圧レベルとの間での切り替りを判定するための判定電圧レベルを記憶する記憶手段(21)と、前記ポジションスイッチから出力された電圧レベルが、前記判定電圧レベルを跨いで変化したときに、当該変化の前後で検出した前記第1電圧レベルと前記第2電圧レベルとの中間の電圧レベルを検出し、当該検出した電圧レベルを前記判定電圧レベルとして前記記憶手段の記憶内容を更新する制御手段(22)と、を備える。

(もっと読む)

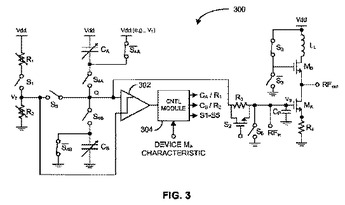

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

101 - 110 / 605

[ Back to top ]