国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

81 - 90 / 99

ヒステリシス型入力回路

【課題】安定したヒステリシス特性を保証し、後段の回路へ不要なパルス波形を伝達しないようにすること。

【解決手段】このヒステリシス入力回路において、ヒステリシス回路10は3つのインバータ40,42,44で構成されている。このヒステリシス回路10内のノードNBは、伝送制御部12の変位検出部14の入力端子に接続されている。変位検出部14は、ノードNBの電圧VBに応じてヒステリシス回路10内の出力反転動作開始のタイミングおよび変位完了タイミングを検出し、信号伝送路上のインバータ50の活性化/非活性化を制御する。

(もっと読む)

半導体集積回路

【課題】回路の動作スピードを保ちつつリーク電流を削減でき、更に論理ゲートの面積増大を抑えることができる半導体集積回路を提供する。

【解決手段】各論理ゲート内に含まれる同一導電型の複数のトランジスタが共通のしきい値特性を有する。例えば、同一導電型のトランジスタには、同程度のしきい値を有する同一種類のトランジスタを用いる。これにより、これらのトランジスタを同一活性領域に近接して形成することが可能になるため、論理ゲートの面積を小さくすることができる。また、図1に示す半導体集積回路は、p型MOSトランジスタまたはn型トランジスタの一方に高しきい値特性のトランジスタを用いた論理ゲート(G1,G2)を有するため、回路を伝播する2相の信号(立ち上がりおよび立ち下り)のうちの何れか一方の信号経路に高しきい値特性のトランジスタを選択的に挿入することが可能になる。

(もっと読む)

デューティ比補正回路

【課題】パルス発生器等から供給されるパルスのデューティ比を補正する回路において、容量を小量化して応答性を向上する。半導体集積回路のチップ面積を小さくする。

【解決手段】PLLoutがデューティ比50%未満だとクロックパルスのデューティ比は50%を上回る。AVR>Vdd/2となってコンパレータ7の出力CoutがHとなり第2のスイッチング増幅回路8がオンする。コンデンサC2によりバイアス信号BIASが高くなる。FET21の電流制御により出力点Q1の信号のパルス幅が長くなる。クロックパルスのデューティ比が低く補正されて50%に近付く。コンデンサ2により積分した信号はFET21,24へのバイアス信号BIASとなるから小電流で済む。コンデンサC2の容量を小さくできる。チップ面積を小さくできる。応答性が向上する。

(もっと読む)

出力バッファ回路

【課題】高スルーレートでスルーレート変動の少ない出力バッファ回路を実現する。

【解決手段】NMOSトランジスタM3をONすることで容量C1と容量C2との容量比で出力トランジスタであるPMOSトランジスタM1のゲート電圧をしきい値電圧以下に低下させ、PMOSトランジスタM1をONさせ、同時に、電流源I1により最終的にPMOSトランジスタM1のゲート電圧を0Vにし、さらに、PMOSトランジスタM4をONすることで容量C3と容量C4の容量比で出力トランジスタであるNMOSトランジスタM2のゲート電圧をしきい値電圧以下に低下させ、NMOSトランジスタM2をONさせ、同時に電流源I2により最終的にNMOSトランジスタM2のゲート電圧を電源電圧レベルにする構成とし、出力トランジスタのゲート電圧を容量分圧制御で行う。

(もっと読む)

信号伝達回路

【課題】 コストダウンの障害となるLDMOS(Laterally Diffused Metal Oxide Semiconductor)の使用数を削減しコストダウンを図れる信号伝達回路を提供する。

【解決手段】 低電位の回路において、パルス発生器11aは信号入力端HINから入力した信号の正負のエッジを検出し、それぞれのエッジを表すパルス信号をスイッチング素子Q1〜2に出力する。スイッチング素子Q1〜2は電流源Ires1〜2をオン/オフし、LDMOSQ3を介して高電位の回路において、抵抗R3に電流を供給する。抵抗R3は電流地に応じた電圧を両端に発生し、異なる閾値を有するインバータInv1〜2によって、低電位の回路にて入力された信号の正負のエッジが復元され、パルス検出回路12a、RS(Reset-Set)フリップフロップ13、スイッチング素子Q5〜6、抵抗R13〜14によって、入力された信号が復元される。

(もっと読む)

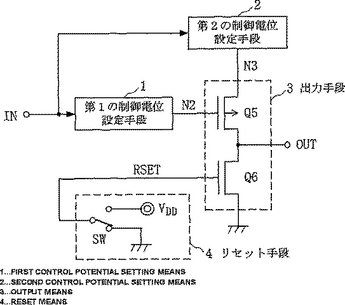

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

高速のターンオン時間を有する電流ミラー

【課題】高速のターンオン時間を供給する電流ミラー回路を提供すること。

【解決手段】電流ミラーがオフであるときに回路の中のノードが第1の電圧に保たれ、それにより、電流ミラー回路がオンに切り換えられるとノード電圧が迅速に必要な電圧に到達することを可能にする。

(もっと読む)

入力ヒステリシスを有する高速スイッチング回路

本発明は、スイッチング回路、並びに、このスイッチング回路の半導体スイッチング素子の閾値電圧を制御する方法に関し、半導体スイッチング素子(Mi)の出力信号から生じる制御信号に応じて半導体スイッチング素子(Mi)のバルク電圧が選択される。これにより、ヒステリシスを有し、クロス電流がより小さく、閾値電圧が正確に調整できる高速スイッチング回路が提供されることができる。  (もっと読む)

(もっと読む)

電流駆動型D/Aコンバータおよびそのバイアス回路

【課題】 電流スイッチトランジスタの制御電圧によって生じるノイズをより小さくし、また、電流スイッチがオフする際に生じていたグランドもしくは電源電圧のノイズを低減し、高性能な電流駆動型D/Aコンバータを得る。

【解決手段】 NMOSトランジスタM12P,M12N,M22P,M22N,M32P,M32Nがオフするオフ制御電圧(BIAS3)を、オン制御電圧(BIAS2)に近づけた電圧に設定したことにより、NMOSトランジスタの制御電圧振幅(オン制御電圧−オフ制御電圧)が小さくなり、寄生容量を介した電荷注入によるノイズの発生を低減すると共に、オフする際の寄生容量からグランドもしくは電源への放電電流の流れ込みによるグランド電圧もしくは電源電圧のノイズの発生を低減し、高性能な電流駆動型D/Aコンバータを得ることができる。

(もっと読む)

81 - 90 / 99

[ Back to top ]