国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

41 - 50 / 99

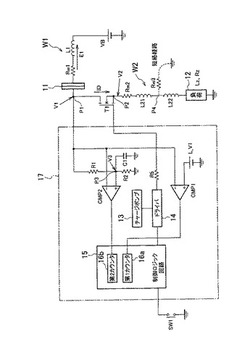

電力供給装置

【課題】配線ショートの発生時とコネクタの接触不良とを区別して回路を保護することが可能な電力供給装置を提供する。

【解決手段】本発明の電力供給装置では、半導体素子T1のドレインの電圧V1が、コンパレータCMP1の同相入力最低電圧を下回る前に半導体素子T1を遮断するので、負荷回路を確実に保護することができる。また、第1判定電圧をL_V1とし、第2判定電圧をV3としたとき、電圧V1が「V1<L_V1」となった場合に、リトライ動作を実行し、「V1<L_V1」となる回数がN1回に達した場合、または、「L_V1<V1<V3」となる回数がN2回に達した場合に、半導体素子T1の遮断状態を保持して負荷回路を保護する。更に、コネクタ11の接触不良に起因して電圧V1が急激に低下した場合には、電圧V1の最低値が安定した値とならず、半導体素子T1の遮断状態は保持されない。

(もっと読む)

入力バッファ回路及びこれを用いた入力装置

【課題】高速低消費電力で閾値制御が可能な入力バッファ回路及び入力装置を提供する。

【解決手段】入力バッファ回路30は、バイアス電圧生成回路100で生成されたバイアス電圧PLV及びこれよりもレベルの高いバイアス電圧NLVにより動作する回路である。この回路30は、バイアス電圧PLVよりも低い第1の電圧が入力されると、オン状態になってその第1の電圧をノードN32から出力するNMOS32と、バイアス電圧NLVよりも高い第2の電圧が入力されると、オン状態になってその第2の電圧をノードN33へ出力するPMOS33と、ノードN32から出力される第1の電圧をラッチして第1の論理の電圧をノードN34へ出力するラッチ回路34と、ノードN33から出力される第2の電圧をラッチして第2の論理の電圧をノードN34へ出力するラッチ回路35とを有している。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の制御方法

【課題】入力信号に必要な振幅を低減する。

【解決手段】電源線L1と出力部N2との間のトランジスタTA1のゲートG1は容量素子C1を介して入力部N1に結合する。電源線L2と出力部N2との間のトランジスタTA2のゲートG2は容量素子C2を介して入力部N1に結合する。トランジスタTB3は、電源線L1からみてゲートG1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB4は、ゲートG1からみて電源線L1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB3の閾値電圧VT3がトランジスタTA1の閾値電圧VT1を上回り、かつ、トランジスタTB3の閾値電圧VT3とトランジスタTB4の閾値電圧VT4との加算が減少するように、トランジスタTB3およびトランジスタTB4の各々のバックゲートBの電位VBが設定される。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

多値出力回路及びこれを用いた液晶駆動装置

【課題】本発明は、小規模な回路構成でありながら、設定電圧の増加や変更にも柔軟に対応することが可能な多値出力回路を提供することを目的とする。

【解決手段】本発明に係る多値出力回路は、デジタル信号(電圧設定信号SET)からアナログ電圧Va〜Vdを生成するデジタル/アナログ変換部3と;電圧選択信号A1に基づいて、アナログ電圧Va〜Vdのいずれか一を選択的に出力する電圧選択部41〜4nと;電圧選択部41〜4nの出力電圧を液晶パネル7に供給するバッファ51〜5nと;を有して成る構成とされている。

(もっと読む)

シュミット回路

【課題】入力信号EAの立ち上がり時の回路しきい値電圧VIH及び立ち下がり時の回路しきい値電圧VILのDC仕様がVDDとVSSとの中心電圧近傍からVSS側又はVDD側に極端に偏っている場合であっても、入力信号EAの立ち上がり時の回路しきい値電圧VIH及び立ち下がり時の回路しきい値電圧VILのDC仕様を満足させることができるシュミット回路を提供する。

【解決手段】PMOSトランジスタ26、27とNMOSトランジスタ28からなる入力部25に対して、PMOSトランジスタ32からなる第1のヒステリシス設定部31と、NOR回路34とPMOSトランジスタ35からなる第2のヒステリシス設定部33とを設ける。

(もっと読む)

出力装置、多値出力装置、及び半導体集積装置

【課題】ディエンファシス時と非ディエンファシス時の消費電流を一定にすることで、電源変動も一定となり、その結果ジッタの低減を可能にする出力装置を提供する。

【解決手段】入力されたデータを振幅制御して出力するデータ出力部1と、第1及び第2の振幅制御信号に基づいて伝送路に電流を重畳出力して伝送信号の振幅を制御する電流駆動部2と、第1及び第2の振幅制御信号に基づいて電流駆動部2との合計消費電流値が略一定となるように消費電流を制御するダミー電流駆動部3と、を備えて構成されている。

(もっと読む)

電圧駆動型半導体素子のドライブ回路及びインバータ装置

【課題】正電圧の電源のみで、導通損失を増加させることなく、誤点弧を防止する電圧駆動型半導体素子のドライブ回路及びインバータ装置を提供する。

【解決手段】半導体素子を駆動するドライブ回路において、直流電源の正側に接続された第1のスイッチと、第1のスイッチの他端子に接続され、かつ直流電源の負側に接続された第2のスイッチと、直流電源の正側に接続された第3のスイッチと、第3のスイッチの他端子に接続された第4のスイッチと、第4のスイッチの他端子に接続され、かつ直流電源の負側に接続された第5のスイッチと、第1のスイッチの他端子と第4のスイッチの他端子に接続されたコンデンサを備え、半導体素子のゲートは第3のスイッチの他端子に接続され、半導体素子のソースは直流電源の負側に接続する。

【効果】正電圧の電源のみで、半導体素子のゲートに負電圧を印加することが可能となる。

(もっと読む)

アナログ信号選択回路

【課題】簡素な回路を用いて構成され、複数のアナログ信号から所望のアナログ信号を選択するアナログ信号選択回路を提供する。

【解決手段】アナログ信号選択回路は、複数のアナログ信号毎に対応して設けられ、対応する上記アナログ信号と基準となる三角波信号とを比較してPWM信号を生成する複数のコンパレータ(2a〜2c)および上記複数のコンパレータが出力するPWM信号を論理演算する論理演算回路(3)を備えるアナログ信号選択回路であって、上記論理演算回路は、全ての上記コンパレータが出力するPWM信号の論理積演算を行って上記複数のアナログ信号のうちの電圧が最大のアナログ信号に相当するPWM信号を生成する。

(もっと読む)

41 - 50 / 99

[ Back to top ]