国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

11 - 20 / 99

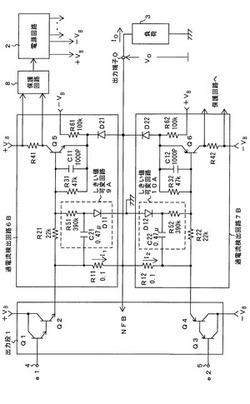

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

過電流保護装置及び過電流保護システム

【課題】同一の電源に接続された複数の過電流保護装置どうしで、リトライ動作を実行するタイミングに時間差を持たせることが可能な過電流保護装置、及び過電流保護システムを提供する。

【解決手段】IC回路51-1のFET(Q1)をオンとした際に、バッテリ電圧VBAが閾値電圧以下となった場合には、各IC回路のFET(Q1)を全てオフとし、更に、FET(Q1)のオンからバッテリ電圧VBAが閾値電圧以下となるまでの時間を計時する。この時間が400μsec未満であれば、カウント値Nをインクリメントする。その後、ランダムに設定された待機時間Tpが経過した後、再度FET(Q1)をオンとする動作を繰り返し、カウント値Nが7に達した時点で、IC回路51-1のFET(Q1)をオフ状態に保持する。従って、デッドショートの発生している負荷駆動用の回路のみを確実に停止させ、それ以外の負荷駆動用の回路の駆動を継続させることができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

電圧変化検知装置

【課題】電界効果トランジスタの閾値電圧がばらついた場合にも、検知電圧のばらつきを低減でき、所望の電圧検知範囲で電圧変化を検知することができる電圧変化検知装置を提供する。

【解決手段】ドレインが電源電位に接続され且つソースが第1のノードにおいて第1の定電流源又は第1の抵抗に接続され且つゲートが固定電位に接続されている第1の電界効果トランジスタと、ドレイン及びゲートが電源電位に接続され且つソースが第2のノードにおいて第2の定電流源又は第2の抵抗に接続されている第2の電界効果トランジスタと、当該第1のノードの電位と当該第2のノードの電位との比較結果に応じて電源電位が所定の検知電位を跨いで変化したことを検知した旨の検知信号を生成する検知信号生成部と、を含む電圧変化検知装置。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

駆動回路、当該駆動回路を具備する表示装置、及び当該表示装置を具備する電子機器

【課題】チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる際、しきい値電圧の変動の程度に応じてしきい値電圧を補正する駆動回路を提供することを課題の一とする。

【解決手段】半導体層の上下に絶縁層を介して配置された第1のゲート及び第2のゲートを有する単極性のトランジスタで構成される駆動回路において、第1のゲートには、トランジスタのスイッチングを制御するための第1の信号が入力され、第2のゲートには、トランジスタのしきい値電圧を制御するための第2の信号が入力され、第2の信号は、トランジスタのソースとドレインとの間を流れる電流を含む、駆動回路の消費電流の値に応じて制御されるものとする。

(もっと読む)

11 - 20 / 99

[ Back to top ]