国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

31 - 40 / 99

楽音信号送信装置及び楽音信号受信装置

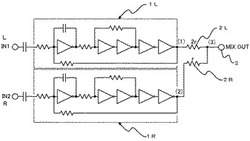

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

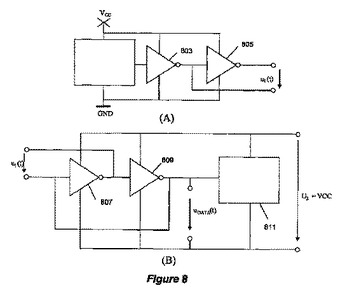

信号処理回路、出力方法、信号処理方法及び信号処理システム

信号処理回路は入力インバータ及び出力インバータを含む。インバータの各々は、入力整流信号を受信する信号入力部と、反転した出力整流信号を提供する信号出力部と、整流されたdc出力電圧を増幅する一対の電圧出力部とを有する。第1の回路入力端子は、入力インバータの出力及び出力インバータの入力に接続される。第2の回路入力端子は、入力インバータの入力及び出力インバータの出力に接続され、信号入力端子はデータの成分を有する入力信号を受信する。電源出力端子のペアがインバータの電圧出力端子に接続され、整流されたdc電源出力を提供する。第1の回路出力端子は或る電源出力端子に接続され、第2の回路出力端子は別の電源出力端子に接続され、それら回路出力端子はデータ成分を有する出力信号を提供する。  (もっと読む)

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、検出すべき電圧を入力する第4の端子と、参照電圧の電位差に応じた電流をそれぞれ流す第1、第2のトランジスタ(以下、Tr)と、第1のTrと直列接続される第3のTrと、第2のTrと直列接続される第4のTrと、第3のTrの流す電流に応じたミラー電流を流す第5のTrと、第4のTrの流す電流に応じたミラー電流を流す第6のTrと、第6のTrと第4の端子との間に接続される第7のTrと、第5のTrと第3の端子との間に接続され、第7のTrの流す電流に応じたミラー電流を流す第8のTrと、を有し、第5、第8のTrの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】電圧検出回路12が、ブリッジ回路Bに供給される交流電圧を分圧した電圧を基準電圧Vrefだけシフトアップした電圧を出力する。第1比較回路13が、電圧検出回路12により出力された電圧と第1比較電圧Vc1とを比較して、ブリッジ回路Bに供給される正の交流電圧の大きさが電圧Vthを越えないように第1トランジスタQ1を制御する。第2比較回路14が、電圧検出回路12により出力された電圧と第2比較電圧Vc2とを比較して、ブリッジ回路Bに供給される負の交流電圧の大きさが電圧Vthを越えないように第2トランジスタQ2を制御する。

(もっと読む)

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】ブリッジ回路Bに対して正電圧を供給する方向に導通するトランジスタQ1が、ブリッジ回路Bと図示しない交流電圧源との間に設けられている。ダイオードブリッジ12が、ブリッジ回路Bと図示しない交流電圧源との間に設けられ、ブリッジ回路Bに供給される交流電圧を全波整流する。比較回路13が、ブリッジ回路Bに供給された交流電圧と電圧Vthとを比較して、ブリッジ回路Bに供給される交流電圧の大きさが電圧Vthを越えないようにトランジスタQ1を制御する。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

ドライバ回路及びドライバIC

【課題】クロスポイントが50%からずれた電気波形を出力する際も、良好な出力波形を維持することができるドライバ回路を得る。

【解決手段】初段増幅段A1、2段目増幅段A2及び最終増幅段A3の3段の差動増幅段が直列に接続されている。初段増幅段A1及び2段目増幅段A2に、クロスポイント調整回路CP1,CP2がそれぞれ接続されている。クロスポイント調整回路CP1は、初段増幅段A1の正相と逆相のDCレベルの少なくとも一方を制御して、初段増幅段A1の出力信号のクロスポイントを調整する。また、クロスポイント調整回路CP2は、2段目増幅段A2の正相と逆相のDCレベルの少なくとも一方を制御して、2段目増幅段A2の出力信号のクロスポイントを調整する。

(もっと読む)

受信回路、電子機器、及び受信回路の制御方法

【課題】 直前の数サイクルに依存して波形が劣化する信号に対して正しく受信することができない。

【解決手段】 本発明の受信回路10は、入力信号を基準電圧と比較して比較結果をハイレベル又はローレベルで出力する比較回路12と、比較回路12の出力レベルを次の1サイクル間保持する第1の記憶回路13と、第1の記憶回路13の出力レベルを次の1サイクル間保持する第2の記憶回路14と、第1の記憶回路13と第2の記憶回路14の出力レベルに応じて前記基準電圧のレベルをサイクル毎に制御する電圧制御回路11を有する。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

31 - 40 / 99

[ Back to top ]