国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

21 - 30 / 99

入力回路

【課題】ヒステリシス電圧や応答速度の電源電圧依存性を緩和し、幅広い範囲の電源電圧条件下で動作するヒステリシス特性を有する入力回路を提供すること。

【解決手段】低電源電圧条件下でヒステリシス電圧が小さくなる回路(PMOSトランジスタ101〜103及び、インバータ501)と、低電源電圧条件下でヒステリシス電圧が大きくなる回路(PMOSトランジスタ101、104及び、インバータ501)とを設けた。

(もっと読む)

半導体装置

【課題】電源回路等を追加することなく、第1の電源電圧が低下してもダイナミックVTによる高速化の効果の低減を抑制できる半導体装置を提供する。

【解決手段】第1の回路は、第1の電源電圧を供給する第1の電源ラインと第1の電源電圧よりも低い第2の電源電圧を供給する第2の電源ライン間に接続された、トランジスタを備える。制御回路は、第1の電源ラインと第2の電源ライン間に接続され、上記トランジスタのバックゲートに第1の電源電圧と第2の電源電圧の電位差よりも振幅が大きい制御信号を供給する。

(もっと読む)

差動増幅器

【課題】入力端子にノイズが発生する。

【解決手段】第1の電流経路は、第1の電源端子と第1の出力端子間に接続され、制御端子に差動入力信号の一方が入力される第1のトランジスタと、第2の電源端子と第1の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第2のトランジスタと、第1の電源端子と第1のトランジスタとの間に接続される第1のスイッチ回路とを有し、第2の電流経路は、第2の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の一方が入力される第3のトランジスタと、第1の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第4のトランジスタと、第2の電源端子と第3のトランジスタとの間に接続される第2のスイッチ回路とを有し、第1、第2のスイッチ回路は、制御信号により導通状態が制御される差動増幅器。

(もっと読む)

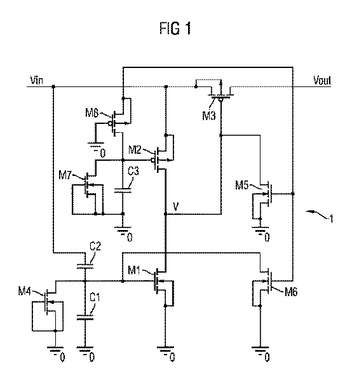

特に圧電式のマイクロジェネレータを有しているエネルギ自立型のマイクロシステムのためのトリガ回路及び整流器

本発明は、十分に大きい電圧レベルを検出するため、また、十分な出力を供給するためのトリガ回路に関する。更に本発明は、従来の解決手段に比べて、同じ出力電圧で効果的により多くの出力を供給する整流器に関する。トリガ回路及び整流回路は、特に圧電式のマイクロジェネレータを有するエネルギ自立型のマイクロシステムにおいて使用することができる。  (もっと読む)

(もっと読む)

フラッシュメモリ

【課題】多値技術を用いたメモリにおいて、複数ページにわたるデータを短時間に転送するフラッシュメモリを提供する。

【解決手段】フラッシュメモリは、各々がnビット(nは2以上の整数)のデータを記憶する複数のメモリセルを含むメモリセルアレイと、メモリセルのゲートに接続された複数のワード線と、メモリセルに接続された複数のビット線と、ビット線を介してメモリセルに記憶されたデータを検出するセンスアンプと、或るワード線に接続されたm個(mは2以上の整数)のメモリセルのそれぞれに格納されたnビットデータを保存するm×nビットのデータラッチと、データラッチから外部へ2ビット以上のデータを同時に転送可能な多値レベルインタフェースとを備えている。

(もっと読む)

半導体集積回路

【課題】ゲート面積を増大させることなく、電界効果トランジスタ間のしきい値電圧のバラツキを自律的に補正させる。

【解決手段】補正回路12は、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より大きい場合、その電気的特性の劣化量の小さい方の半導体素子の劣化を進行させ、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より小さい場合、その電気的特性に差のある半導体素子の劣化を所定の周期ごとに交互に進行させる。

(もっと読む)

電子回路

【課題】 充電回路の動作を安定化させる。

【解決手段】 充電回路(100)は、第1出力信号を出力するTr制御回路(24)と、第1出力信号が入力されて動作するトランジスタ(Tr)及びコンデンサ(C1)と、その状態を検出し、その結果としての第2出力信号を出力するコンパレータ(21)と、第2出力信号に基づいて、Tr制御回路をして前記第1出力信号を出力させるかどうかを決定する第3出力信号をTr制御回路に供給するフリップフロップ(24)と、を備え、フリップフロップの入出力特性の遷移帯は、Tr制御回路の入出力特性の遷移帯と重ならない。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続された第1のPMOSトランジスタQ1と、ゲート端子が入力端子INに接続され、ソース端子がトランジスタQ1のドレイン端子に接続され、ドレイン端子が出力端子OUTに接続された第2のPMOSトランジスタQ2と、ゲート端子が出力端子OUTに接続され、ソース端子がトランジスタQ1のドレイン端子とトランジスタQ2のソース端子との接続点に接続され、ドレイン端子が接地電位に接続された第3のPMOSトランジスタQ3と、第1の端子が出力端子OUTに接続され、第2の端子が接地電位に接続された電流制限部I1とから構成される。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続され、ドレイン端子が出力端子OUTに接続された第1のPMOSトランジスタQ1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電流制限部I1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電荷蓄積部C1とから構成される。電流制限部I1の電流値は、サブマイクロアンペア以下に設定される。

(もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

21 - 30 / 99

[ Back to top ]