国際特許分類[H03L7/22]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528) | 二つ以上のループを用いるもの (73)

国際特許分類[H03L7/22]の下位に属する分類

パルス計数器または分周器を有するもの

国際特許分類[H03L7/22]に分類される特許

1 - 10 / 73

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

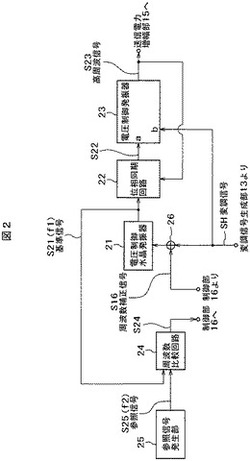

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

周波数補正回路

【課題】送信波の周波数に同期された周波数又はその逓倍波を容易かつ正確に出力できる周波数補正回路を提供する。

【解決手段】第1電圧制御発振器16の出力信号と基準発振信号との位相差に応じた位相差信号を第1位相比較器10により生成し、第1ループフィルタ12を介して第1位相差信号に応じた第1発振制御信号により第1制御発振器16の発振をフィードバック制御する第1フェーズロックループ回路106と、第2電圧制御発振器36の出力信号と比較対象信号との位相差に応じた位相差信号を第2位相比較器30により生成し、第2ループフィルタ32を介して第2位相差信号に応じた第2発振制御信号により第2制御発振器36の発振をフィードバック制御する第2フェーズロックループ回路114とを備え、第1発振制御信号に応じて第2発振制御信号を変動させることによって比較対象信号に応じて出力信号をロックする。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

1 - 10 / 73

[ Back to top ]