国際特許分類[H04L25/03]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | ベースバンド方式 (1,966) | 細部 (1,421) | 送信機または受信機における整形回路網,例.整形回路網を付加するもの (399)

国際特許分類[H04L25/03]の下位に属する分類

受動整形回路網

国際特許分類[H04L25/03]に分類される特許

41 - 50 / 399

判定帰還型波形等化器

【課題】直前ビットの受信判定データを利用することなく、第1ポストカーソルのISIを補正する判定負帰還型波形等化器を提供する。

【解決手段】判定帰還型波形等化器は、受信データを入力する増幅回路と、フリップフロップを含み、増幅回路の出力がフリップフロップに入力され、フリップフロップにより増幅回路の出力を判定するデュオバイナリ信号判定器と、フリップフロップに保持された判定結果を逐次シフトさせるシフトレジスタと、シフトレジスタの各出力を入力とし、出力を増幅回路の出力に帰還し、その電位を制御する複数の電流制御ブロックとを有し、フリップフロップに保持された判定結果をシフトレジスタでシフトさせることなく増幅回路の出力の出力に帰還しない。

(もっと読む)

光受信方法、光受信装置及びビート雑音推定器

【課題】本発明は、ビットパターンのゆらぎによる影響を小さくすることにより、ビート雑音推定器の推定誤差を小さくすることができる技術を提供することを目的とする。

【解決手段】本発明のビート雑音推定器13は、光電変換器11が出力する受信電気信号91に時間遅延を与える遅延子21と、遅延子21が時間遅延した受信電気信号91から最尤判定器12が出力する信号成分推定値92を減算して受信電気信号91から信号成分を除去した雑音信号95を出力する減算器22と、減算器22が出力する雑音信号95と最尤判定器12が出力する信号成分推定値92との相関関係から算出した補正前のビート雑音推定値を、最尤判定器12が出力するビート雑音推定対象である複数の信号成分についての信号成分推定値92の乗算値から算出した擬似的なビート雑音推定値で補正した値を、補正後のビート雑音推定値93として出力する相関器23と、を備える。

(もっと読む)

2値化回路、復調回路、及び車載チューナ

【課題】2値化回路の回路規模を縮小する。

【解決手段】コンパレータ176は、入力電圧と基準電圧とを比較し、比較結果を出力する。第1充放電回路172は、入力電圧と基準電圧との差である差分電圧に第1充放電係数を乗算することにより、第1電圧を生成し、第2充放電回路173は、差分電圧と所定の閾値電圧との差に第1充放電係数より大きい第2充放電係数を乗算することにより、第2電圧を生成し、制御回路174は、差分電圧と閾値電圧とを比較し、比較結果に基づいて第2充放電回路173のオン及びオフを切り換える。第2充放電回路173がオフの場合には、1クロック前の基準電圧と1クロック前の第1電圧との和が新しい基準電圧としてコンパレータ176に供給され、第2充放電回路173がオンの場合には、1クロック前の基準電圧と1クロック前の第1電圧と1クロック前の第2電圧との和が新しい基準電圧としてコンパレータ176に供給される。

(もっと読む)

受信回路

【課題】消費電力及びノイズを低減することができる受信回路を提供することを課題とする。

【解決手段】入力データをサンプリングすることによりデジタルデータを出力するサンプリング回路(401)と、前記サンプリング回路により出力されたデジタルデータに対して無限インパルス応答フィルタを用いて等化処理を行う等化回路(402)と、前記等化回路により等化処理されたデータの位相を検出する位相検出回路(404)と、前記位相検出回路の出力信号に対してフィルタリングを行う第1のフィルタ(405)と、前記第1のフィルタの出力信号を基に前記無限インパルス応答フィルタのフィードバックするデータのビット数を調整する制御回路(403)とを有する受信回路が提供される。

(もっと読む)

駆動回路および光送信装置

【課題】駆動対象の応答特性を柔軟に補償すること。

【解決手段】駆動回路100は、分岐部110と、遅延部121,122と、増幅器131,132と、合成部140と、を備えている。分岐部110は、駆動信号を分岐する。遅延部121,122は、遅延量が可変の可変遅延部を含み、分岐部110によって分岐された各駆動信号をそれぞれ遅延させる。増幅器131,132は、各駆動信号のうちの一部の駆動信号を反転させる。合成部140は、遅延部121,122および増幅器131,132の後段に設けられ各駆動信号を合成する。

(もっと読む)

受信装置

【課題】少ないビット数のADCを用いながら、信号受信精度を維持することが可能な受信装置を提供する。

【解決手段】第1クロック信号に同期して、NRZ方式の受信信号をサンプリングして得られるサンプル値と当該サンプル値の直前のサンプル値との差分を量子化する第1アナログ/デジタル変換器と、第1クロック信号とは位相が異なる第2クロック信号に同期して、受信信号をサンプリングして得られるサンプル値を量子化する第2アナログ/デジタル変換器と、第1アナログ/デジタル変換器の出力の変化に基づいて、受信信号で表される受信データを復元するデータ判定部と、第2アナログ・デジタル変換器の出力とデータ判定部で復元された受信データとに基づいて、受信信号の同期信号と第1クロック信号および第2クロック信号との位相ズレを抽出する位相検出部と、位相ズレに基づいて、第1クロックおよび第2クロックの位相を調整する位相調整部とを備える。

(もっと読む)

受信回路、信号伝送回路、及び信号受信方法

【課題】単相で振幅が小さいクロック信号を的確に検出可能な受信回路を提供する。

【解決手段】受信回路は、第1端と第2端との間をAC結合するAC結合回路22と、第1端に印加される第1の信号に応じて第2端に現れる第2の信号をローパスフィルタリングして第3の信号を生成するローパスフィルタ回路23,25と、第2の信号と第3の信号とが入力されるコンパレータ21とを含む。

(もっと読む)

光受信装置

【課題】光分離部による分離ペナルティの発生を防止し、変調方式に対する依存性をなくし、実装上の容易性を確保した光受信装置を提供すること。

【解決手段】光入力信号を複数の経路に分離する光分離部(11)と、分離後の光入力信号を電気信号に変換する光電気変換部(12a,12b)と、光電気変換部(12a,12b)から出力された電気信号を所定のしきい値(Vth1,Vth2)に基づいて識別した識別結果を出力する識別器(13a,13b)と、識別器(13a,13b)から出力された識別結果に基づいて所定の演算を行う演算回路(14)とを備える。

(もっと読む)

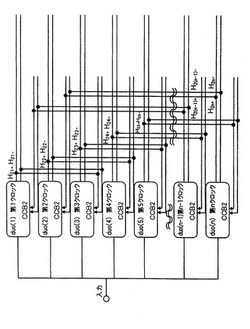

データ受信装置および適応等化回路

【課題】回路規模を抑制し、消費電力を低減する。

【解決手段】複数の受信回路2a〜2dは、伝送線路に接続され、伝送線路からデータ信号を受信する。受信回路2a〜2dは、受信したデータ信号の波形を整形するための等化器を具備している。適応等化回路3は、複数の受信回路2a〜2dの全部または2以上の所定数ずつに対して1つ設けられ、対応した受信回路2a〜2dの等化器の、波形整形をするための等化係数を算出し、対応した受信回路2a〜2dに出力する。

(もっと読む)

受信装置

【課題】受信レベルが変動する場合であっても、正確に信号を復調することが可能な受信装置を提供する。

【解決手段】マンチェスタ符号化またはサブキャリア変調された受信信号を、復調部において1ビット間の時間平均が0となる参照信号を受信信号と乗算して1ビット長にわたって積分して得られる相関値を閾値と比較して復調する。

(もっと読む)

41 - 50 / 399

[ Back to top ]