国際特許分類[H04L25/03]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | ベースバンド方式 (1,966) | 細部 (1,421) | 送信機または受信機における整形回路網,例.整形回路網を付加するもの (399)

国際特許分類[H04L25/03]の下位に属する分類

受動整形回路網

国際特許分類[H04L25/03]に分類される特許

31 - 40 / 399

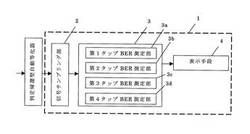

判定帰還型自動等化器評価装置および判定帰還型自動等化器評価方法

【課題】従来の判定帰還型自動等化器(DFE)の評価装置では、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

(もっと読む)

パルスパターン発生装置及び該装置を用いた誤り率測定システム並びにパルスパターン発生方法

【課題】発生できるパルスパターンの種類を増やす。

【解決手段】差動クロック発生部4は、所定周期の正相クロックと、正相クロックと位相が反転した反転クロックとを発生する。クロック選択部5は、差動クロック発生部4が発生する正相クロック又は反転クロックの何れかのクロックを選択する。データ保持部3は、クロック選択部5で選択された正相クロック又は反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力する。パルスパターン発生部7は、データ保持部3から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生する。

(もっと読む)

プログラム可能な、レシーバの等化回路および方法

【課題】伝送媒体によって起こる減衰を好適に補償する等化回路を提供する。

【解決手段】伝送媒体を介して送信されるデータ信号は、その伝送媒体によって起こる減衰をこうむる。等化回路(106)は、直列に配列される複数のステージ(202)を含み、それによって、ステージ(202)の周波数応答を共に統合することを可能にする。各ステージ(202)は、ゼロを挿入するようにプログラム可能であり得、それによって、ステージ(202)の周波数応答の大きさは、20dB/decade大きくなる。ゼロの周波数位置はまた、プログラム可能であり得、それによって、各ステージ(202)が、特定の周波数に対する特定の量のゲインを与えることを可能にする。各ステージ(202)は、高周波ノイズの低減およびクロストーク消去に対する極の位置を決定するようにプログラム可能でもあり得る。

(もっと読む)

受信回路

【課題】補間誤差を低減することができる受信回路を提供することを課題とする。

【解決手段】受信回路は、入力データ信号をクロック信号に基づいてサンプリングしてサンプリング信号を出力するサンプリング回路(201)と、前記入力データ信号に対する前記サンプリング信号の位相情報に基づいて前記サンプリング信号を補間して補間データ信号を出力するデータ補間回路(202)と、前記サンプリング信号と前記位相情報とに基づいて補間誤差を出力する補間誤差判定回路(203)と、前記補間誤差に基づいて設定される等化係数によって前記補間データ信号を等化し、前記等化された補間データ信号を判定して判定信号を出力する判定等化回路(204)と、前記判定信号又は前記等化された補間データ信号に基づいて前記位相情報を生成し、前記データ補間回路及び前記補間誤差判定回路に前記位相情報を出力する位相検出回路(205)とを有する。

(もっと読む)

受信回路、送信回路、通信システム、及び通信システムの送信設定方法

【課題】信号遷移発生用の符号化を用いることなくデータとクロックとを1つの信号に纏めて送受信可能な送信回路及び受信回路を提供する。

【解決手段】送信回路は、データ信号とクロック信号とを重み付け加算することにより生成した信号を送信する。また受信回路は、受信した第1の信号の信号遷移からクロック信号を抽出するクロック抽出回路と、抽出されたクロック信号を第1の信号から減算することにより第2の信号を生成する減算回路と、抽出されたクロック信号に応じたタイミングにおいて第2の信号をデータ判定するデータ判定回路とを含む。

(もっと読む)

信号伝送システムおよび半導体回路

【課題】受信回路の負荷容量が変化しても、スルーレートの低下の抑制とリンギングの抑制を両立させることが可能な信号伝送システムを提供する。

【解決手段】送信回路からの信号を配線を通じて受信回路へ伝送する信号伝送システムであって、前記送信回路を実装する第1の基板上において、前記配線に対して直列に接続された第1のRC並列回路と、前記受信回路を実装し、前記第1の基板に着脱可能である第2の基板上において、前記配線に対して直列に接続された第2のRC並列回路とを備えることを特徴とする。

(もっと読む)

メモリ制御回路及びそれを用いたデータ伝送システム

【課題】送信機、受信機の双方において新たな入力端子を設ける必要がないデータ伝送システムを提供すること。

【解決手段】本発明に係るメモリ制御回路は、それぞれが第1及び第2の入力端子を備え、各前記第1の入力端子に外部メモリから受信したデータ信号が入力される複数のコンパレータと、前記外部メモリから受信した差動ストローブ信号の正相及び逆相の双方から、各前記第2の入力端子に入力される複数の基準電圧を生成する基準電圧発生回路と、を備えるものである。

(もっと読む)

信号波形の品質改善方式

【課題】電子計算機およびその周辺機器に接続された通信用ケーブルの長さに応じて、良好な波形品質が確保できるように通信信号の波形を調整する。

【解決手段】通信用ケーブルにケーブルの長さを識別可能なID情報を保存したメモリを内蔵し、電子計算機または周辺機器に搭載された制御用マイコンが通信用ケーブルのID情報を読み出し、読み出したID情報から通信用ケーブルの長さを判別し、通信用LSIを良好な波形品質を得られるように設定する。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

バースト受信機,バースト受信制御方法、およびシステム

【課題】 ONU毎にレーザ立上り時間Tonが異なるバースト信号を受信しても、利得切替を確実にバーストプリアンブル期間に制限し、BER劣化を防ぐことを目的とする。

【解決手段】 OLTは、バースト信号毎にトランスインピーダンスアンプの利得切替許容期間を設定し、常に最適な利得切替許容期間となるよう制御する。具体的には、ONU登録時にONUから通知されたTonとONU識別子の対応を保持し、受信するバースト信号毎にTon時間に基づいて適切な切替許可時間Tselを決定し、トランスインピーダンスアンプの利得切替を許容する期間を設定する。

(もっと読む)

31 - 40 / 399

[ Back to top ]