ローム株式会社により出願された特許

1,111 - 1,120 / 3,539

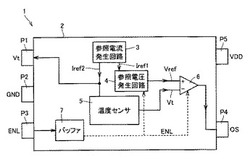

半導体装置

【課題】低消費電流の半導体装置を提供する。

【解決手段】このサーモスタットIC1では、目標温度に応じたレベルの一定の参照電圧Vrefを発生する参照電圧発生回路4と、検出温度に応じたレベルの電圧Vtを出力する温度センサ5と、参照電圧Vrefと電圧Vtの高低を比較し、比較結果を示す信号を出力する比較回路6とを備え、参照電圧発生回路4および比較回路6の活性化/非活性化の制御が可能になっている。したがって、全部の回路を常時活性化させていた従来に比べ、消費電流が小さくて済む。

(もっと読む)

利得調整回路およびD級電力増幅器

【課題】利得調整および広範囲な電圧源にも安定して適用することができる利得調整回路およびD級電力増幅回路を提供する。

【課題を解決するための手段】

利得調整回路100はアナログ入力信号が入力される信号入力端子102、アナログ信号を増幅し電圧源E1が供給される演算増幅器108、演算増幅器108の反転入力端子108aと出力端子108cとの間に接続される第1のT型抵抗回路T123を備える。信号入力端子102と反転入力端子108aとの間に利得調整するための第1の可変抵抗RV1を接続する。演算増幅器108の非反転入力端子108bにはバイアス電圧供給回路130から直流バイアス電圧が供給される。バイアス電圧供給回路130は第1の電圧生成回路132および第2のバイアス電圧生成回路138を備える。第1のバイアス電圧生成回路132は第2の電圧源E2および第2のT型抵抗回路T123aを備え、第2のバイアス電圧生成回路138は第3の電圧源E3および第2の可変抵抗RV2を備える。

(もっと読む)

半導体発光素子

【課題】結晶欠陥の発生を防止し、特性が劣化しない範囲で、TMモード発振が行えるようにした半導体発光素子を提供する。

【解決手段】GaAs基板1上に、n型AlGaAsクラッド層2、n型AlGaAsビーム拡散層3、n型AlGaAs光ガイド層4、MQW活性層5、p型AlGaAs光ガイド層6、p型AlGaAsビーム拡散層7、p型AlGaAs第1クラッド層8、InGaPエッチングストップ層9、p型AlGaAs第2クラッド層10、p型GaAsコンタクト層11が形成されている。MQW活性層5は、バリア層と引っ張り歪を持つ井戸層で構成された多重量子井戸構造を有しており、井戸層の各膜厚がバリア層の各膜厚よりも大きく、井戸層のうち、少なくとも1層の膜厚が他の井戸層とは異なるように構成されている。

(もっと読む)

犠牲層のエッチング方法、MEMSデバイスの製造方法およびMEMSデバイス

【課題】被覆膜で被覆された犠牲層をエッチングするときに、エッチングによる被覆膜の損傷の発生を抑制できる犠牲層のエッチング方法、該エッチング方法を用いたMEMSデバイスの製造方法および該製造方法により製造されるMEMSデバイスを提供すること。

【解決手段】シリコン基板2上に犠牲酸化膜29を形成し、犠牲酸化膜29を、シリコン基板2の一方面に対向する対向部17と、シリコン基板2の一方面に形成された段差部19と、対向部17と段差部19とを連設する側部18とを有する表面膜11で被覆する。次いで、側部18に、犠牲酸化膜29とのエッチング選択比が、表面膜11の犠牲酸化膜29とのエッチング選択比よりも大きい材料からなる保護膜16を形成する。そして、犠牲酸化膜29をエッチングして、表面膜11をシリコン基板2との間に中空部分を有する状態で支持される中空支持膜とすることにより、シリコンマイク1を得る。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体発光素子

【課題】アクセプタ層のアクセプタ不純物濃度を高めることなく、発光素子の輝度上昇が図れる半導体発光素子を提供する。

【解決手段】ZnO基板1上に、アンドープZnO層2、窒素ドープMgZnO層3、透明導電膜4が順に積層されている。透明導電膜4上にp電極5が、ZnO基板1の裏面にはn電極6が形成されている。ここで、窒素ドープMgZnO層3のバンドギャップが、アンドープZnO層2のバンドギャップよりも0.2eV以上大きくなるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】機能素子の可動部分を配置した空間の気密性の低下を抑制しつつ、小型化を実現できる半導体装置とその製造方法を提供する。

【解決手段】表面10aに凹部15が形成され、その凹部15内に配置された可動部分を有する機能素子100を備える変位検出用半導体チップ10と、変位検出用半導体チップ10の表面10a上で凹部15を囲んで環状に配置されたダイアタッチ材を含む結合部20と、可動部分の変位を検出した機能素子100が出力する検出信号を処理する処理回路300を有し、空洞を形成するように凹部15の上方を覆って結合部20上に配置された信号処理用半導体チップ30とを備え、結合部20によって凹部15が気密封止されている。

(もっと読む)

半導体レーザ装置

【課題】装置の大型化を抑えつつ、高出力化を図ることが可能な半導体レーザ装置を提供すること。

【解決手段】レーザ光を出射する複数の半導体レーザ素子と、上記複数の半導体レーザ素子が設けられたブロック1B、およびこのブロック1Bに対して上記レーザ光の出射方向反対側に位置するベース1Aを含むステム1と、ブロック1Bと導通するコモン用リード34と、上記複数の半導体レーザ素子と導通する複数のリード31A,31B,32A,32Bと、を備えた半導体レーザ装置Aであって、ベース1Aは、複数のリード31A,31B,32A,32Bを挿通させる貫通孔11,12を有しており、複数のリード同士31A,31B,32A,32Bが互いに絶縁されるように、貫通孔11,12には絶縁材料6が充填されている。

(もっと読む)

半導体レーザ装置

【課題】半導体レーザ素子を適切に保護することが可能な半導体レーザ装置を提供すること。

【解決手段】半導体レーザチップ2と、x方向において半導体レーザチップ2を挟む1対の側壁部31を有する樹脂パッケージ3と、を備える半導体レーザ装置A1であって、1対の側壁部31には、x方向において互いに離間する2対の受入面32aを有する嵌合受入部として2対の凹部32のが設けられており、樹脂パッケージ3は、平面視において半導体レーザチップ2を覆うとともに、1対の受入面32a間に圧入された嵌合挿入部としての2対の凸部36を有するカバー35をさらに有する。

(もっと読む)

半導体装置

【課題】全体の小型化を図る場合であっても、樹脂パッケージにクラックが発生する虞れが少なく、かつ所望箇所への面実装も適切に行なうことが可能な半導体装置を提供する。

【解決手段】半導体チップ1と、この半導体チップ1の電極に電気的に接続された複数の導体2A,2Bと、これら複数の導体2A,2Bおよび半導体チップ1を封止する樹脂パッケージ3と、を有しており、導体2A,2Bは、厚みが相違する厚肉部21a,21bと薄肉部22a,22bとを有し、かつ厚肉部21a,21bの下面部が樹脂パッケージ3の底面から露出した面実装用の端子部23a,23bとされている、半導体装置Aであって、複数の導体2A,2Bのうちの少なくとも1つの厚肉部21a,21bは、その全体または一部の幅が不均一な非矩形状に形成されている。

(もっと読む)

1,111 - 1,120 / 3,539

[ Back to top ]