富士通セミコンダクター株式会社により出願された特許

1,131 - 1,140 / 2,507

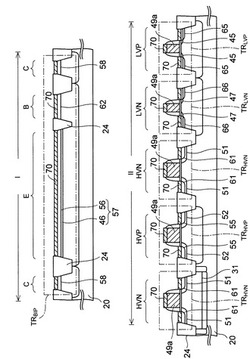

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

描画データ処理方法、図形描画システム、及び図形描画データ作成プログラム

【課題】効率的な描画データ処理方法を提供する。

【解決手段】描画データ処理方法は、第1のデータについて入出力データ形式に応じた第1のデータ生成処理を選択し、第2のデータについて入出力データ形式に応じた第2のデータ生成処理を選択し、少なくとも第1のデータ及び第2のデータの出力データ形式に応じて各頂点間のメモリアドレス距離を示すオフセットを計算し、第1のデータ生成処理を第1のデータに対して実行することにより、出力形式の第1のデータを複数の頂点について生成し、生成した第1のデータを前記オフセットが示す間隔でメモリに書き込み、第2のデータ生成処理を第2のデータに対して実行することにより、出力形式の第2のデータを複数の頂点について生成し、生成した第2のデータを前記オフセットが示す間隔でメモリに書き込む各段階を含むことを特徴とする。

(もっと読む)

動画像符号化装置及び動画像符号化プログラム

【課題】符号化でマルチパスを用いることのできないリアルタイム処理では、シーンチェンジ後のレート制御パラメータの初期化に固定的に定めた初期値を使わざるを得ず、レート制御パラメータの最適値への収束が遅くなり、発生情報量的に不利であり、画質が不安定になりやすい。

【解決手段】初期パラメータ設定部は、シーンチェンジ発生時、シーンチェンジとなったフレームとその次のフレームとの差分をSAD演算部から取得し、データベースから該差分に最も近い差分絶対値和の移動平均に対応するレート制御パラメータを読み出す。読み出したレート制御パラメートと、レート制御パラメータ初期値記憶部に記憶されたレート制御の各方式に応じたレート制御パラメータの初期値との中間の値をレート制御パラメータ現在値記憶部に格納し、差分絶対値和の移動平均に対応するレート制御パラメータをレート制御部におけるレート制御のパラメータに反映(初期化)する。

(もっと読む)

半導体集積回路及び半導体集積回路の故障診断方法

【課題】CPUのパフォーマンスに影響を及ぼすことなく、故障診断を行うことを可能にする半導体集積回路を提供する。

【解決手段】通常動作において利用される第1のバスBUSA、及びそれとは異なる第2のバスBUSAに接続されたCPU1から第2のバスを介して出力される診断情報に基づいて、診断マクロ6が誤り検出情報を求め、プログラムの実行に応じて求められた最終の誤り検出情報と保持している1つの期待値との比較によりCPUが故障しているか否かを判定するようにして、通常動作に利用される第1のバスの負荷を増加させずに、故障診断を行えるようにする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体基板に欠陥が入るのを防止すること。

【解決手段】シリコン基板20に素子分離溝20aを形成する工程と、素子分離溝20a内に素子分離絶縁膜23を形成する工程と、素子分離絶縁膜23を形成した後、シリコン基板20に不純物を注入する工程と、不純物を注入した後、素子分離絶縁膜23とシリコン基板20のそれぞれの上面に、シリコン基板20の反りを抑制するカバー膜26を形成する工程と、カバー膜26が形成された状態で、シリコン基板20をアニールする工程とを有する半導体装置の製造方法による。

(もっと読む)

メモリコントローラ、システムおよび半導体メモリのアクセス制御方法

【課題】 半導体メモリのアクセス効率を向上し、システムの性能を向上する。

【解決手段】 並べ替え判定部は、半導体メモリのアクセス単位である少なくとも1つのメモリブロックをラップアクセスするためのアクセス要求アドレスが、メモリブロックの先頭アドレスと異なるときに並べ替え信号を活性化する。アドレス変換部は、並べ替え信号が活性化されたときに、メモリブロックの先頭アドレスをアクセス開始アドレスに設定する。リードデータ並び替え部は、並べ替え信号が活性化されたときに、アクセス開始アドレスに応じて半導体メモリから順次に読み出されるリードデータを、アクセス要求アドレスに対応するリードデータを先頭にして並び替える。バス出力部は、並び替えられたリードデータを外部リードバスに出力する。この結果、半導体メモリのアクセス効率を向上でき、システムの性能を向上できる。

(もっと読む)

復調回路、復調方法、及び受信システム

【課題】時間差の大きなマルチパスを含む環境において正しい遅延プロファイルを取得可能な復調回路を提供する。

【解決手段】復調回路は、受信信号にFFTを施し複数のキャリアの信号を出力するFFT部と、前記FFT部が出力する前記複数のキャリアの信号から第1の変調方式で変調された第1の信号と第2の変調方式で変調された第2の信号とを含む少なくとも2つの信号を選択して出力する出力選択部と、前記出力選択部が出力する前記第1の信号の信号値に応じて得られる第1の伝送路特性値と前記出力選択部が出力する前記第2の信号の信号値に応じて得られる第2の伝送路特性値とを含む伝送路特性値をIFFTするIFFT部と、前記伝送路特性をIFFTして得られた信号に応じて前記FFTの窓の位置を制御するFFT窓制御部を含む。

(もっと読む)

電源装置

【課題】

低負荷状態でも高い電力効率で電圧変換を行うことができる電源装置を提供する。

【解決手段】

入力電圧を所定の出力電圧に変換する電源装置において入力電圧端子と基準電源との間に直列に接続された第1のスイッチM1及び第2のスイッチM2と,第1,第2のスイッチの接続ノードLXと出力端子Outとの間に設けられたインダクタLoutと,出力端子の出力電圧に応じて第1,第2のスイッチを交互にオン,オフ制御する制御ユニット1と,接続ノードの電圧が基準電源の電圧以上になる第1の状態と,接続ノードの電圧が基準電源の電圧より低い比較電圧以上になる第2の状態とを検出するコンパレータユニット15とを有する。そして,制御ユニットは,コンパレータユニットによる第2の状態の検出に応答して,第2のスイッチの抵抗を増加させ,コンパレータユニットによる第1の状態の検出に応答して,第2のスイッチをオフにする。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】部分回路に関する相関のない複数種類の特性情報がそれぞれの特性の規格値を遵守し、部分回路の改善を図ること。

【解決手段】設計支援装置500は、検出部502により設計対象回路200から部分回路を構成する任意のデータパスとデータパスに対応するクロックパスを検出し、選択部503により検出されたデータパスおよびクロックパス上のセル群から対象セルを選択し、対象セルを、置換部504により当該対象セルと同一機能で特性が異なるセルに置換する。置換された後のセルの特性に基づいて当該対象セルを含むパスの複数種類の特性分布を取得部505により取得し、判断部507により複数種類の特性分布がそれぞれの制約に違反しているか否かを判断する。

(もっと読む)

クロック生成回路、電源供給システム及び遅延時間調整部

【課題】一方のクロック信号に対して他方のクロック信号の立ち上がりを遅延させる遅延時間を制御するため、例えば電波状況に応じて、輻射ノイズの低下を図るクロック生成回路、電源供給システム及び遅延時間調整部を提供すること。

【解決手段】コントロール部16は、ワンセグ受信機2から受信したBERデータDBに基づいて、ワンセグ受信機2のビットエラーレートを最も小さくするような、第1及び第2基準クロック信号Ck1,Ck2の周波数の設定周波数データDf、及び、第1基準クロック信号Ck1に対する第2基準クロック信号Ck2の立ち上がりの遅延時間の設定遅延時間データDtに設定し、その設定周波数データDf及び設定遅延時間データDtを基準クロック生成回路21に出力する。基準クロック生成回路21は、入力された設定周波数データDf及び設定遅延時間データDtに基づいて、第1及び第2基準クロック信号Ck1,Ck2を生成する。

(もっと読む)

1,131 - 1,140 / 2,507

[ Back to top ]