富士通セミコンダクター株式会社により出願された特許

2,411 - 2,420 / 2,507

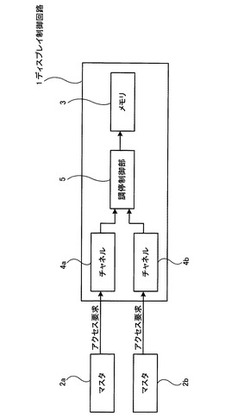

ディスプレイ制御回路およびディスプレイ装置

【課題】簡易な構成で調停を行うことができる。

【解決手段】ディスプレイ制御回路1は、複数のマスタ2a、2bとの間でディスプレイに画像を表示する条件を規定した属性情報をやり取りする回路である。ディスプレイ制御回路1は、属性情報を格納するメモリ3と、マスタ2a、2bに対応して設けられ、マスタ2a、2bのメモリ3へのアクセス要求を受け付ける複数のチャネル4a、4bと、ハードウエアで構成され、各チャネル4a、4bが受け付けたアクセス要求を調停し、選択した1つのアクセス要求のメモリ3へのアクセスを許可する調停制御部5と、を有する。

(もっと読む)

半導体集積回路及びコード割り当て方法

【課題】本発明は、多くの数の機能及び多くの数のオプションを指定可能なコード割り当てに対応する構成の設定レジスタを有する半導体集積回路を提供することを目的とする。

【解決手段】半導体集積回路は、複数の端子と、複数の端子から入力される複数のビットのうちの一部である第1の所定数のビットにより一意に特定されると、複数のビットから第1の所定数のビットを除いた残りのビットのうちの少なくとも一部である第2の所定数のビットを格納する第1のラッチと、複数の端子から入力される複数のビットのうちの一部である第3の所定数のビットにより一意に特定されると、複数のビットから第3の所定数のビットを除いた残りのビットのうちの少なくとも一部である第4の所定数のビットを格納する第2のラッチを含み、第1の所定数と第3の所定数とは異なり、第2の所定数と第4の所定数とは異なることを特徴とする。

(もっと読む)

スイッチトキャパシタ積分回路及びデルタシグマA/D変換器

【課題】本発明は、少数の参照電圧値で動作するSC積分器を提供することを目的とする。

【解決手段】SC積分回路は、差動増幅器と、差動増幅器の出力端と第1の入力端との間に結合される第1の容量素子と、第1の入力電圧と第1の参照電圧との間に第1のサイクルにおいて結合され第2の参照電圧と第1の入力端との間に第2のサイクルにおいて結合される第2の容量素子と、第3の参照電圧及び第4の参照電圧のうち選択信号に応じて選択された一方の電圧と第1の参照電圧との間に第1のサイクルにおいて結合され第3の参照電圧と第1の入力端との間に第2のサイクルにおいて結合される第3の容量素子と、第3の参照電圧及び第4の参照電圧のうち選択信号に応じて選択された一方の電圧と第1の参照電圧との間に第1のサイクルにおいて結合され第4の参照電圧と第1の入力端との間に第2のサイクルにおいて結合される第4の容量素子を含むことを特徴とする。

(もっと読む)

モジュール配置方法、モジュール配置プログラム、及びLSI設計装置

【課題】本発明の課題は、半導体集積回路を構成するモジュールを配置する際、外部端子位置との接続性に基づくモジュールへの割当領域の決定後、更にその割当領域の重心を求めて接続端子としたモジュール間の接続性に基づいてモジュールを配置することを目的とする。

【解決手段】上記課題は、LSIチップを構成する複数のモジュールを配置するモジュール配置方法であって、コンピュータが、モジュール毎の外部端子位置と前記LSIチップ上の任意の領域との接続性の相関値を算出し、その算出結果に基づいて各モジュールへ割り当てる割当領域を決定する割当領域決定手順と、各モジュールへ割り当てられた前記割当領域から算出される各重心を接続端子としてモジュール間の接続性を含めた相関値を算出し、その算出結果に基づいてモジュール位置を決定するモジュール位置決定手順とを実行することを特徴とするモジュール配置方法により達成される。

(もっと読む)

半導体装置の製造方法

【課題】本発明は複数の半導体装置を積層して三次元構造として実装密度の向上を図るのに好適な半導体装置の製造方法に関し、再配線基板の両面に半導体装置を確実に搭載することを課題とする。

【解決手段】インターポーザ21の第1の面に第1の半導体素子3−1が搭載され、この第1の面の反対側の第2の面に第2の半導体素子3−2が搭載された半導体装置の製造方法であって、前記インターポーザ21の第1の面に第1の半導体素子3−1を搭載する工程と、インターポーザ21を裏返し第1の半導体素子3−1が収容される凹部を有した治具30上にインターポーザ21を載置する工程と、緩衝部材31によりインターポーザ21の撓みを防止しつつ、インターポーザ21の第2の面に第2の半導体素子3−2を搭載する工程とを有する。

(もっと読む)

半導体回路設計方法、マスクデータ変換方法、及び半導体マスクデータ作成方法

【課題】本発明の課題は、タイミング検証結果と関連付けてOPC精度を変更することを目的とする。

【解決手段】本発明の課題は、半導体回路設計をシミュレーションする半導体回路設計方法であって、コンピュータが、レイアウトデータを参照してパス毎に遅延余裕度を算出する遅延余裕度算出手順と、前記遅延余裕度が光近接効果補正の精度を落とせる範囲内である場合に、該当するセル毎に高精度の光近接効果補正が不要であることを示す高精度不要情報を生成する高精度不要情報生成手順とを実行することにより達成される。

(もっと読む)

半導体装置

【課題】パッケージ化され放熱体を備えた半導体装置であって、前記放熱体により熱を放散する一方、パッケージ全体の厚さを厚くすることなく、反り又は歪み等の変形を軽減することができる構造を有する半導体装置を提供する。

【解決手段】半導体装置20は、配線基板21と、前記配線基板21上に配設された半導体素子22と、前記配線基板21上の電極と、前記半導体素子22の電極パッドとを接続する複数のボンディングワイヤ23と、前記配線基板21上で、前記半導体素子22の一部及び前記複数のボンディングワイヤ23を封止する樹脂25と、前記樹脂25上に配設された放熱体26と、を有し、前記放熱体26は、前記ボンディングワイヤ23の配設箇所に面している部位が他の部位よりも厚さが薄く形成されていることを特徴とする。

(もっと読む)

半導体装置の設計方法及び半導体装置

【課題】本発明の課題は、回路設計段階における配線のダミー発生時に半導体の積層構造による下層からの段差影響を吸収するように配線することによって、上層への段差影響を抑止することを目的とする。

【解決手段】上記課題は、コンピュータが半導体の回路設計に係るレイアウトデータを作成する半導体レイアウトデータ作成方法であって、該コンピュータが、前記レイアウトデータから下層の配線データを参照し、該下層の配線の配線幅に応じて、該下層の配線の領域に相当する処理層の領域にダミー配線データを発生させるダミー発生手順を実行することを特徴とする半導体レイアウトデータ作成方法により達成される。

(もっと読む)

DC−DCコンバータおよびその制御方法

【課題】 DCMで動作する場合にもハイサイド側を確実に導通するDC−DCコンバータおよびその制御方法を提供すること。

【解決手段】 DC−DCコンバータは、電源電圧VBに至る経路およびローサイドトランジスタFET1のドレインに至る経路の間に接続されるカップリング容量のローサイドトランジスタFET2のドレイン側の端子および接地電位の間に接続されるスイッチ部と、ハイサイドトランジスタFET1の導通に先立ち、スイッチ部を導通し、ハイサイドトランジスタFET1の導通に同期して、スイッチ部を非導通にするローサイド側nchFET制御回路10と、を備えることを特徴とする。

(もっと読む)

半導体集積回路およびシステム

【課題】 内部回路の動作に伴う内部電源電圧の変動を抑制し、内部回路の動作マージンを向上する。

【解決手段】 内部回路は、内部電源電圧を受けて動作する複数の回路ブロックを有する。内部電圧制御回路は、動作する回路ブロックの組み合わせに応じて、複数のレギュレータ制御信号を生成する。複数のレギュレータは、レギュレータ制御信号の活性化に応答してそれぞれ動作し、外部電源電圧を用いて内部電源電圧を生成する。例えば、動作する回路ブロックの数が多くなると動作するレギュレータの数が増える。このように、内部回路の実際の動作に合わせてレギュレータ制御信号を生成し、レギュレータの動作を制御することにより、内部電源電圧の変動を最小限にできる。この結果、半導体集積回路の動作マージンを向上でき、半導体集積回路の歩留を向上できる。

(もっと読む)

2,411 - 2,420 / 2,507

[ Back to top ]