株式会社ルネサステクノロジにより出願された特許

1,011 - 1,020 / 4,790

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

制御装置

【課題】簡易な処理でノイズによる誤動作を低減できる制御装置を提供する。

【解決手段】デジタル回路10全体にわたって複数の箇所に配置された複数のノイズモニタ11により得られたノイズに関するアナログ量は、アナログ/デジタル変換器12により最大デジタル量へ変換され、周波数/電圧制御回路40へ入力される。周波数/電圧制御回路40は、最大デジタル量のうち基準デジタル量を上回るものが一つでもあった場合には、電源電圧がNGであると判定し、クロック発生装置20から出力されるクロックの周波数やレギュレータ30から出力される電源電圧を変更しない。

(もっと読む)

半導体装置およびその製造方法

【課題】ビア配線の配置が界面方向にずれた場合でも、隣り合う配線間でTDDBや短絡が生じる事を防止できる半導体装置を提供する。

【解決手段】この半導体装置は、半導体基板1上に形成された絶縁層(5,11,13,21からなる部分)内に、第1配線7と、第1配線7の上方に配置された第2配線15aと、第1配線7と第2配線15aとを接続するビア配線17とを備え、ビア配線17の上面S1が第2配線15aの上面S2よりも低く配置される。

(もっと読む)

半導体集積回路装置

【課題】シリーズレギュレータ回路の保護動作をメインループ外で行うことにより、信頼性を向上させながら、安定した電源電圧を生成する。

【解決手段】シリーズレギュレータ回路の出力素子であるレギュレーション用トランジスタ4の前段に各種の保護動作による電流制限などの制御を行う入力電流調整部2が設けられている。これにより、メインのシリーズレギュレータ回路の回路構成を単純にすることができ、位相特性調整の自由度が大幅に向上し、電源IC1を安定動作させることができるとともに、緻密な保護動作制御を行うことができる。

(もっと読む)

半導体装置

【課題】半導体装置の受信部に小占有面積と消費電力が小さく且つ良好な受信品質とを得る。

【解決手段】受信して周波数変換された信号のDCオフセットを除去するハイパスフィルタ(10,15)は、CRフィルタを有し、CRフィルタの抵抗素子に流れる電流を選択的に増やすことによってハイパスフィルタの入力インピーダンスを大きくするブートストラップ回路(36)を備える。WCDMA又はHSDPA方式に応じてハイパスフィルタの遮断周波数を切換える。WCDMAによる受信のときはブートストラップ回路を非活性として遮断周波数を高くする。HSDPAによる受信のときはブートストラップ回路を活性として遮断周波数を低くする。CRフィルタ回路の抵抗素子に電流を流すブートストラップ回路を採用することによりCRフィルタ回路のチップ占有面積の増大を抑えて低いカットオフ周波数を実現することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度実装が必要な電子部品の実装形態において、他の半導体装置からのノイズに悪影響を受けることなく、かつ自身のノイズを外部に出さない電磁波ノイズ対策シールド付きパッケージを既存の組み立てプロセスを用いて製造し、安価に提供できる技術を提供する。

【解決手段】積層した半導体チップからなる半導体チップ構造体2の上部に配置した中継基板4と、平面で半導体チップ構造体2を取り囲むようにBGA基板1に配置されたGND端子1cを通してBGA基板1内部のGND層とをボンディングワイヤ5a〜5dで電気的に接続することで、BGA基板1の中心を垂直に貫く直線方向をZ方向、基板の対角線方向をそれぞれX方向、Y方向とした場合のシールドループを形成し、X、YおよびZの3方向の電磁波ノイズを遮蔽する。

(もっと読む)

半導体装置

【課題】微細な抵抗値の調整が可能な抵抗素子を有しかつ小型の半導体装置を提供する。

【解決手段】第1の抵抗素子R1は第1のシート抵抗を有する第1の薄膜F1を含んでいる。第1の抵抗素子R1に直列接続される第2の抵抗素子R2の複数の単位セルPは、同一の長方形状によって外縁が区画された平面パターンであり、第2の薄膜F2と絶縁部IPとを含んでいる。第2の薄膜F2は、長方形状の第1の角部C1に位置する第1の端子領域T1と、第1の角部と対角線に沿って対向する第2の角部C2に位置する第2の端子領域T2と、第1および第2の端子領域T1,T2を繋ぐ線状領域とに設けられている。第2の薄膜F2は第1のシート抵抗よりも小さい第2のシート抵抗を有している。絶縁部IPは長方形状の第3および第4の角部C3,C4を含むように設けられている。

(もっと読む)

連想記憶装置

【課題】連想記憶装置において、消費電力及びピーク電流を削減する。

【解決手段】メモリコントローラ100は、それぞれTCAMセルであるPCAMセル1及びNCAMセル1における検索動作の前に、マッチラインMLpを電源に接続しかつマッチラインMLnを接地した後、マッチラインMLpとマッチラインMLnとを接続し、マッチラインMLpとマッチラインMLnの電位を互いに等しくする。

(もっと読む)

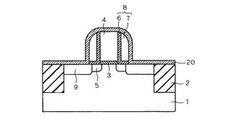

半導体装置およびその製造方法

【課題】リーク電流の増大や被膜性の劣化やトランジスタ特性の劣化等のエッチングに伴う不具合を防ぐことが可能な半導体装置およびその製造方法を提供する。

【解決手段】CMOSトランジスタ500は、ゲート電極202を有するN型MOSトランジスタおよびゲート電極201を有するP型MOSトランジスタを同一の半導体基板1上に備え、ゲート電極202は、ゲート絶縁膜5と多結晶シリコン層61と金属層62と多結晶シリコン層63とを含み、ゲート電極201は、ゲート絶縁膜5と金属層62と多結晶シリコン層63とを含む。

(もっと読む)

半導体装置及びデータ処理システム

【課題】中央処理装置に負担をかけずに短時間で送受信回路の通信条件を変更することができる半導体装置を提供する。

【解決手段】通信条件が初期設定される通信条件設定レジスタ(42,44)とは別に、別の通信条件データが設定可能にされる変更用レジスタ(45,44)を別に設け、中央処理装置(3)により送信から受信等に通信状態を変更する指示が予め与えられているとき、送信状態の終了を検出することにより変更用レジスタの値を通信条件設定レジスタに格納して、通信を行う送受信制御部(20)を採用する。

(もっと読む)

1,011 - 1,020 / 4,790

[ Back to top ]