Fターム[2H092JA33]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | 厚さ規定 (269)

Fターム[2H092JA33]に分類される特許

141 - 160 / 269

表示装置

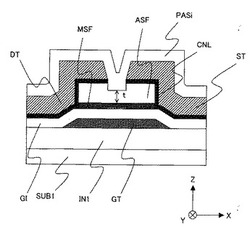

【課題】結晶性シリコン薄膜トランジスタのオフ電流を低減させ、表示コントラストを向上させることが可能な表示装置を提供する。

【解決手段】基板SUB1上に形成されるゲート絶縁膜GIを介してゲート電極GTの上層に形成される第1の半導体層MSFと、第1の半導体層MSFの上面に形成され、凹部が形成される第2の半導体層ASFとからなる活性層と、凹部を挟んで対向配置される一対のコンタクト層CNLと、コンタクト層CNLの一方の上層に形成されるドレイン電極DTと、他方の上層に形成されるソース電極STと、活性層の上面及び前記ドレイン電極DTと前記ソース電極STの上面に連続して形成される保護膜PASiとを有する薄膜トランジスタを備え、凹部が形成されている領域の膜厚は160nm以上である装置。

(もっと読む)

液晶表示装置及び当該液晶表示装置を具備する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供する。

【解決手段】ゲート電極と、ゲート電極と重なるように設けられたゲート絶縁層及び酸化物半導体層と、酸化物半導体層の一部と重なるソース電極及びドレイン電極と、を有する薄膜トランジスタが、画素部に配設される信号線と画素電極との間に設けられており、薄膜トランジスタのオフ電流は、1×10−13A以下であって、液晶素子に並列した容量素子を設けずに液晶容量のみで電位を保持することが可能となり、画素部には画素電極と接続される容量素子が形成されていない構成の液晶表示装置とする。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好で信頼性の高いトランジスタをスイッチング素子として用い、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】加熱処理により脱水化または脱水素化され、表面にナノ結晶からなる微結晶群が形成された酸化物半導体層を形成し、酸化物半導体層上に非晶質で透光性のある酸化物導電層を用いてソース電極層及びドレイン電極層を形成し、酸化物半導体層上の酸化物導電層を選択的にエッチングすることで透光性のあるボトムゲート型のトランジスタを形成し、同一基板上に駆動回路部と画素部を設けた信頼性及び表示品質の高い半導体装置を作製する。

(もっと読む)

半導体装置及びその作製方法

【課題】信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ10

10dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置、表示装置及び電子機器

【課題】電気特性が良好で信頼性の高い薄膜トランジスタ及び当該薄膜トランジスタをスイッチング素子として用いた表示装置を提供することを課題とする。

【解決手段】チャネル形成領域に酸化物半導体を用いたチャネル保護型の薄膜トランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、チャネル形成領域の表層部にはナノクリスタルで構成された結晶領域を有し、その他の部分は非晶質、または非晶質領域中に微結晶が点在した非晶質と微結晶の混合物で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるN型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置の作製方法

【課題】基板処理の効率を高めることができ、また半導体膜の移動度を高めることができるレーザー結晶化法を用いた半導体製造装置を提供する。

【解決手段】半導体膜を成膜する成膜装置と、レーザー装置とを備えたマルチチャンバー方式の半導体製造装置であり、レーザー装置は、被処理物に対するレーザー光の照射位置を制御する第1の手段と、レーザー光を発振する第2の手段(レーザー発振装置1213)と、前記レーザー光を加工または集光する第3の手段(光学系1214)と、前記第2の手段の発振を制御し、なおかつ第3の手段によって加工されたレーザー光のビームスポットがマスクの形状のデータ(パターン情報)に従って定められる位置を覆うように前記第1の手段を制御する第4の手段とを有する。

(もっと読む)

シフトレジスタ及び表示装置

【課題】シフトレジスタ又は該シフトレジスタを有する表示装置の消費電力を低減すること。

【解決手段】シフトレジスタは、クロック信号が1本の配線によって供給されるのではなく、複数の配線によって供給される。さらに、該複数の配線のいずれか一は、シフトレジスタの動作期間を通してクロック信号を供給するのではなく一部の期間においてのみクロック信号を供給する。そのため、クロック信号の供給に伴い駆動される容量負荷を低減することができる。その結果、シフトレジスタの消費電力を低減することができる。

(もっと読む)

液晶表示装置

【課題】クロストーク等が生じにくい、電力消費量が小さい、静電破壊を防止した、液晶表示装置を提供する。

【解決手段】第1絶縁基板2上において、行列状に配置された複数の走査電極8および複数の信号電極9と走査電極8と信号電極9との交点近傍に配置された複数の画素電極10と、各走査電極8と各信号電極9と各画素電極10に接続された各スイッチング素子11と、第1絶縁基板上に配置された複数の第1共通電極C1〜C220と、各画素電極10と各第1共通電極C1〜C220との間に接続された各補助コンデンサ12と、各第1共通電極C1〜C220に接続された第2共通電極13とを備え、各走査電極8と第2共通電極13との交点において、両基板8,13との間に、第1絶縁層および第2絶縁層が積層された。

(もっと読む)

液晶表示装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成することにより、開口率を上げる。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

TFT−LCDアレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】前記アレイ基板の製造方法は、ゲートラインとゲート電極を含むパターンを形成するステップと、活性層と、データラインと、ソース電極と、ドレイン電極とを含むパターンを形成するするとともに、上記パターン以外の領域のゲート絶縁層を除去するステップと、露光・現像により、感光樹脂層に第1ビアホールと、第2ビアホールと、第3ビアホールとを含むパターンを形成するステップと、第3ビアホールを介してドレイン電極に接続する画素電極と、第1接続電極と、第2接続電極とを含むパターンを形成するステップと、を備える。

(もっと読む)

電気光学装置、その製造方法、および電子機器

【課題】画素欠けや、輝度ムラなどの表示不良を低減した表示装置を提供すること。

【解決手段】1つのダミー画素Pdに対して、複数のダミーコンタクトホールDcが形成されており、1つはダミー画素遮光膜9dの角部に配置され、2つは走査線83の幹線に沿って角部のダミーコンタクトホールと連続して配置されている。換言すれば、ダミーコンタクトホールDcは、ダミー領域における第1遮光膜としての走査線83に沿って形成されており、走査線83近傍の下地絶縁膜12の強度を下げる役割を荷っている。つまり、後続の層間絶縁膜の形成工程において熱衝撃が加わった場合、ダミーコンタクトホールDcが形成されたダミー画素領域における走査線83部分が、衝撃吸収部分として機能することになる。よって、有効画素領域における画素欠けや、輝度ムラなどの表示不良を低減することができる。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素部と駆動回路が設けられ、画素部の第1の薄膜トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する保護絶縁層と、保護絶縁層上に画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、保護絶縁層、及び画素電極層は透光性を有し、駆動回路の第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電材料である。

(もっと読む)

微結晶半導体膜及び薄膜トランジスタの作製方法

【課題】結晶性の高い微結晶半導体膜を作製する。また、電気特性が優れ、信頼性の高い薄膜トランジスタ、及びそれを有する表示装置を生産性高く作製する。

【解決手段】プラズマCVD装置の処理室に設けられた複数の凸部を備える電極から、シリコンまたはゲルマニウムを含む堆積性気体を導入し、高周波電力を供給し、グロー放電を発生させて、基板上に結晶粒子を形成し、該結晶粒子上にプラズマCVD法により微結晶半導体膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】酸化物半導体層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、該酸化物絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。また、チャネル保護層に重ならないようにソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層上の絶縁層が酸化物半導体層と接する構成とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層と、ゲート電極層上に設けられるゲート絶縁層と、ゲート絶縁層上に設けられる第1の酸化物半導体層と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置およびその作製方法

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

141 - 160 / 269

[ Back to top ]